## MC 602

## Circuitos Lógicos e Organização de Computadores

IC/Unicamp

**Prof Mario Côrtes**

# Capítulo MC10

Conceitos: Via de Dados e Processadores

m1ps: meu primeiro processador simples (minúsculo MIPS)

# Tópicos

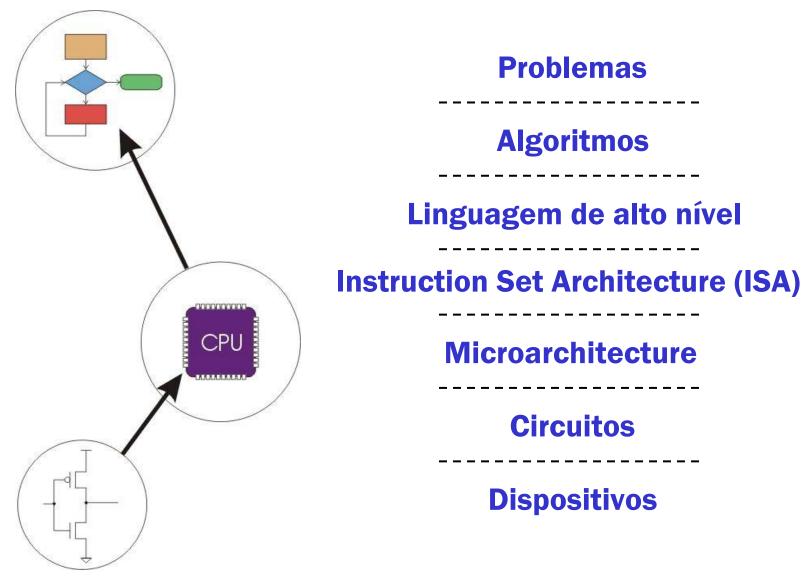

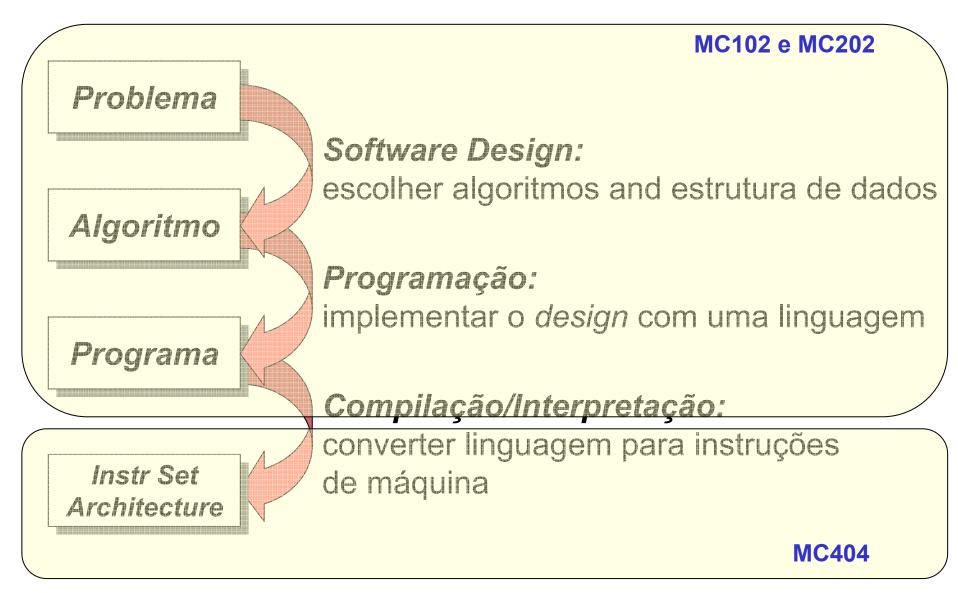

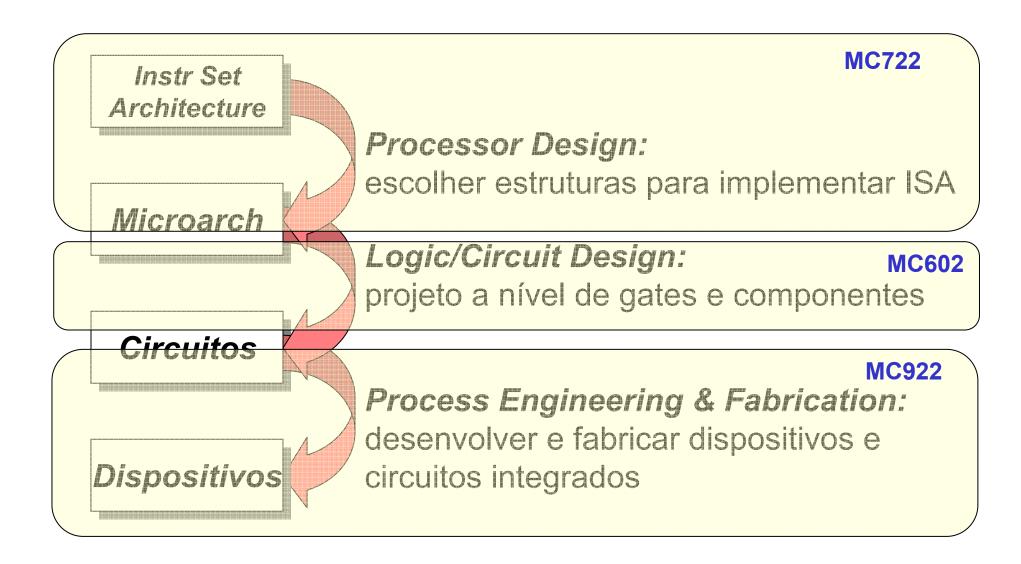

- Níveis de abstração

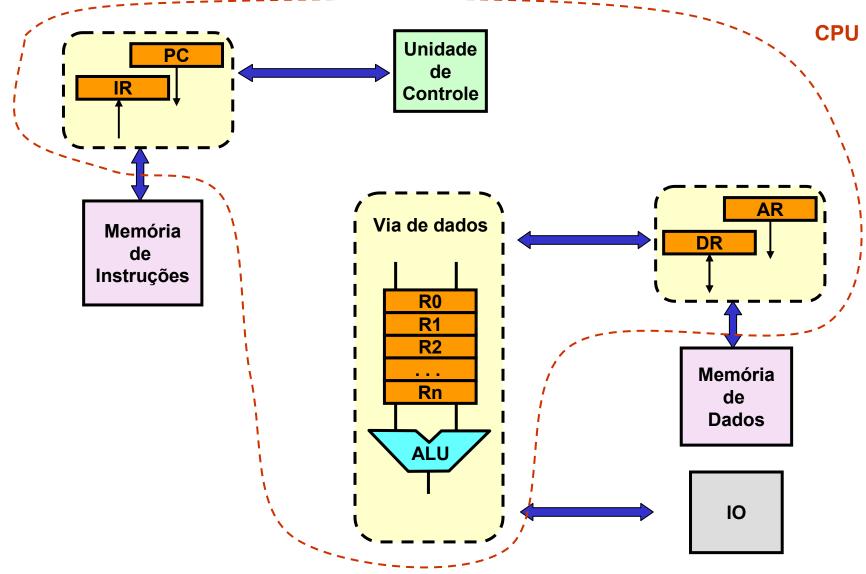

- Máquina de programa armazenado / Von Neumann / Harvard

- m1ps

- Specs

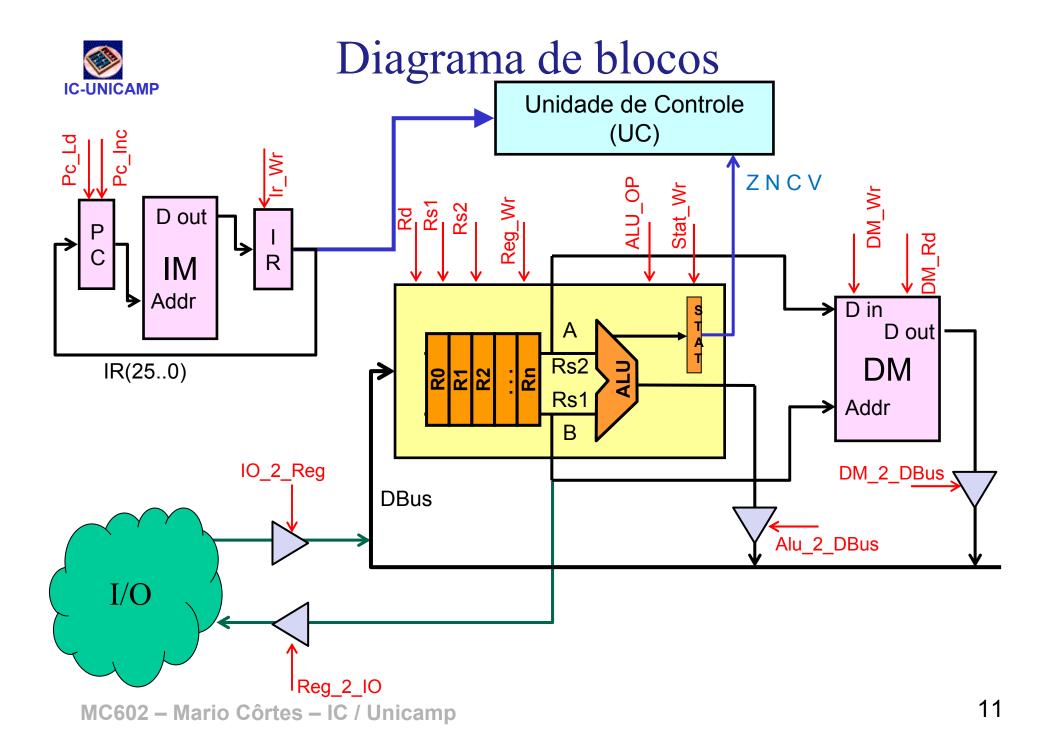

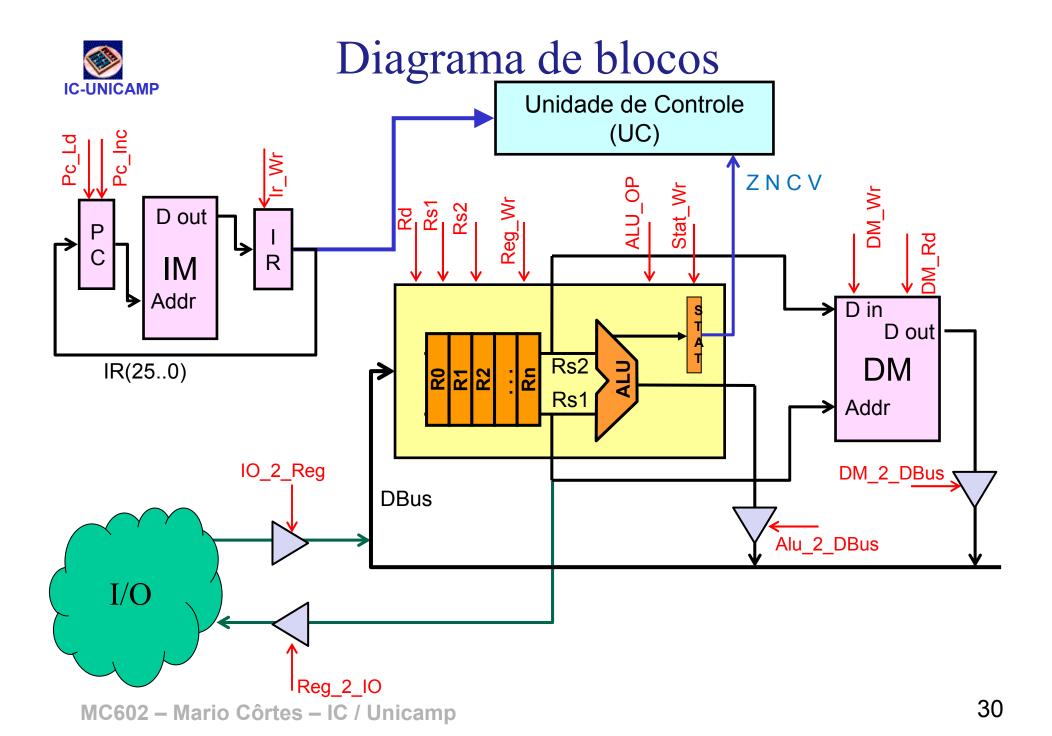

- Diagrama de blocos: via de dados, controle, banco de processadores, memória

- Conjunto de instruções (ISA / instruction set architecture)

- Visão geral de funcionamento

- Visão introdutória: uma máquina Load / Store

- ISA

- Via de dados e controle

## Níveis de abstração

# Níveis de abstração

## Níveis de abstração . . . .

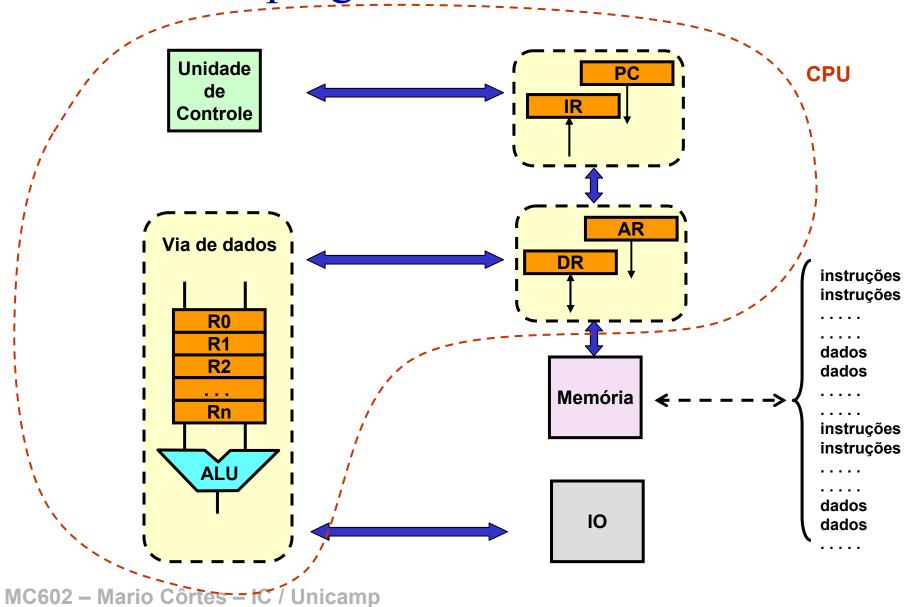

# Von Neumann: computador de programa armazenado

# Arquitetura de Harvard: memórias dedicadas DM e IM

## Objetivos deste capítulo

- Dado o conhecimento do projeto de estruturas: lógica combinacional, lógica sequencial, memórias, FSM

- Introdução:

- como combinar essas estruturas para construir um processador

- Apresentar um processador simples

- m1ps: meu primeiro proc simples (minúsculo MIPS)

# Objetivos do m1ps

- Primeira exposição à organização de processadores

- Conceitos principais, sem ser exaustivo

- Simples, mas não mínimo (pouca complexidade)

- Modular, intelegível, intuitivo, apreensível

- (quase) Completo: possível de implementar códigos básicos

- Extensível

- Uso de algumas estruturas iguais ou próximas ao MIPS

## Specs de implementação

- Dados e instruções de 32 bits

- Endereço de dados e instruções: palavras

- Banco de registradores = MIPS

- ALU: quase igual à do MIPS

- Registrador de status/condição (Z, C, N, V)

- Desvio condicional (status) e incondicional com endereço imediato completo (simplicidade)

- Formatos de instrução iguais ao MIPS

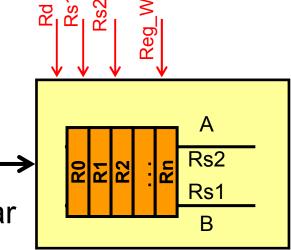

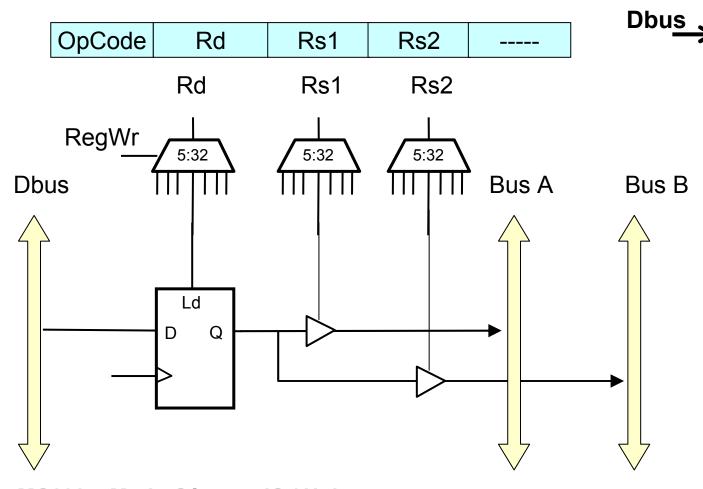

Módulos: banco de registradores

- Parte da via de dados

- 32 registradores de 32 bits

- ATENÇÃO: R0 =0

- permite pseudo instruções move e clear

- Entrada: Barramento Dbus (32 bits)

- Saídas: Barramentos A e B (32 bits)

- Controle

- Rs1 e Rs2 (5bits): selecionam registradores → saídas

A e B

- Rd (5bits): seleciona registrador a ser escrito

- Reg\_Wr (1b): controle de escrita

# Banco de registradores: implementação

Um FF de um registrador

Rs2

Rs1

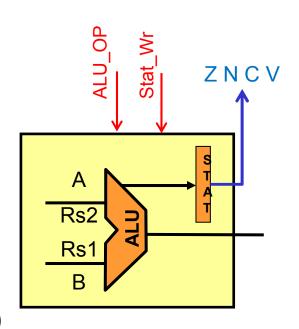

## Módulos: ALU

- Parte da via de dados

- Operações lógicas e aritméticas de operandos de 32 bits: add, sub, and, or

- Dados

- Entradas: Barramentos A e B (32 bits)

- Saídas: ALU\_out (32 bits)

- Controle

- AluOp: define operação da ALU (ver conj de instruções)

- Z,C,V,N: bits de status da operação

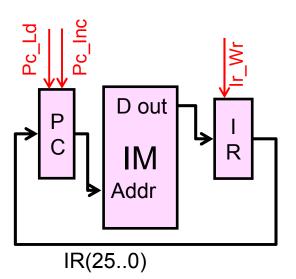

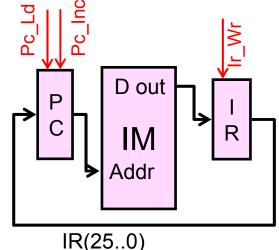

# Módulos: sistema de memória de instruções (IM)

- IM (somente leitura): 2<sup>26</sup> linhas de 32b de largura

- Dados: leitura da instrução (32 bits) → IR

- Endereço: PC (26 bits)

- Controle: leitura sempre

- PC

- Dados: incremento ou carga paralela

- Controle:

- PC-Inc: PC ← PC + 1

- PC-Ld: PC ← Target Address

- carga paralela de endereço de desvio (26 bits)

- cuidado com a temporização

- limitar tamanho na implementação DE1 (< 2<sup>26</sup> linhas )

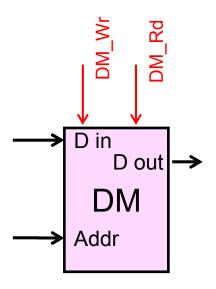

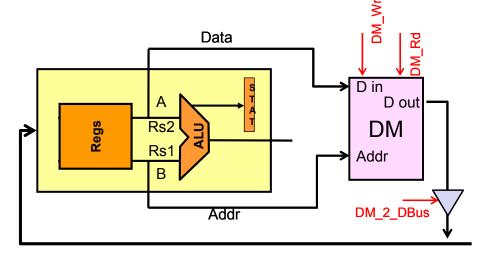

# Módulos: sistema de memória de dados (DM)

- DM: 2<sup>32</sup> linhas de 32b de largura

- sem Regs dedicados para dados e endereço

- Dados:

- saída Dout (32b) é um dos sinais a acionar o DBus

- entrada Din (32b): saída A do banco de registradores (definido por Rs2)

- Endereço: vem de Rs1

- entrada Addr (32b): saída B do banco de registradores (definido por Rs1)

- Controles (1b): DM\_Wr e DM\_Rd

- Observações:

- cuidado com a temporização

- limitar tamanho na implementação DE1 (< 2<sup>32</sup> linhas )

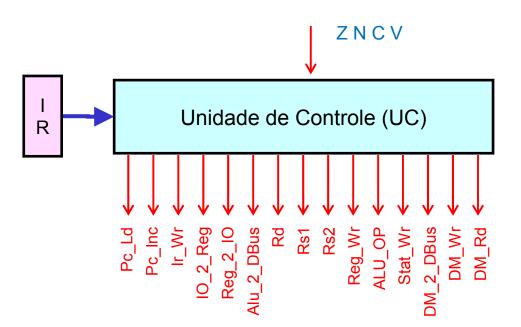

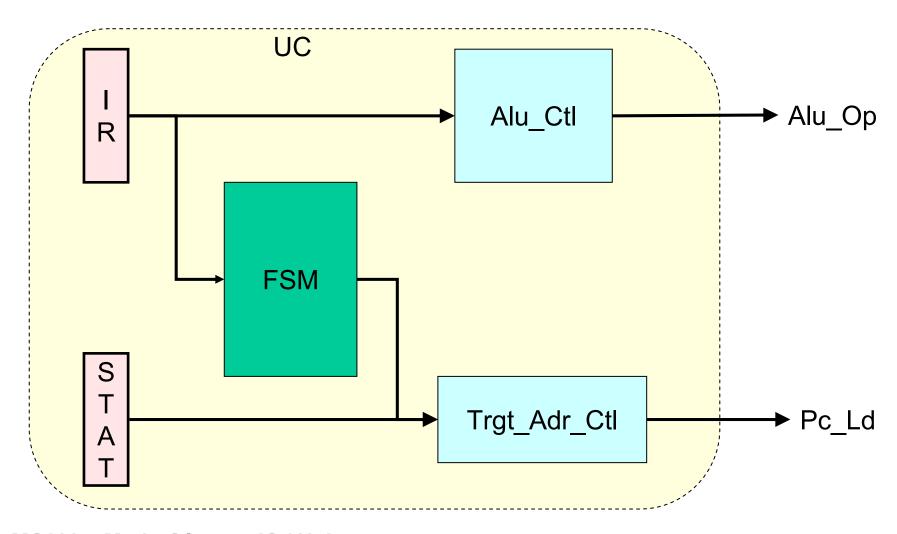

## Módulos: Unidade de controle

### Interfaces

- Entradas: IR e Status

- Saídas: 15 sinais de controle

#### Estrutura

- Principal: FSM

- Apoio:

- lógica para controle de desvio

- lógica para controle da ALU

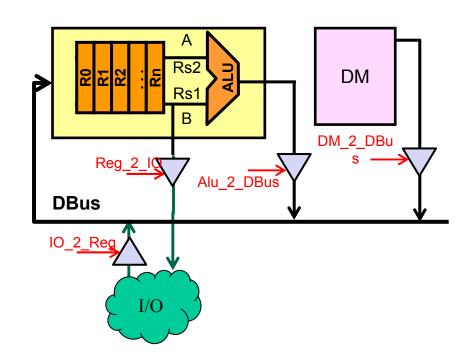

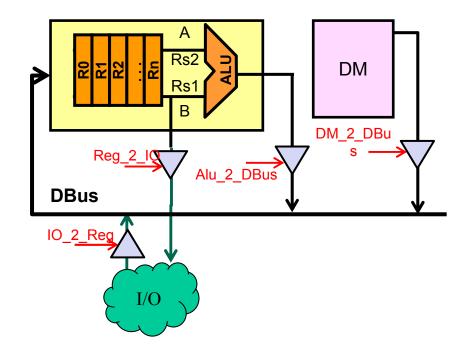

## Módulos: DBus e I/O

- I/O

- In: I/O → Reg, via DBus

- Out: Reg → I/O

- DBus

- 32 bits

- Acionam o barramento:

- DM, saída da ALU, I/O in

- Leem do barramento

- Banco d registradores

# ISA: código de máquina

#### Instruções Formato R, lógicas e aritméticas

|     |     |      |     | Op(3126) | Rd(2521) | Rs1(2016) | Rs2(1511) | Unused(100) |

|-----|-----|------|-----|----------|----------|-----------|-----------|-------------|

| add | Rd, | Rs1, | Rs2 | 001 000  |          |           |           | -           |

| sub | Rd, | Rs1, | Rs3 | 001 001  |          |           |           | -           |

| and | Rd, | Rs1, | Rs4 | 001 010  |          |           |           | -           |

| or  | Rd, | Rs1, | Rs5 | 001 011  |          |           |           | -           |

|     |     |      |     | 6        | 5        | 5         | 5         | 5           |

|    |              | 0   | bs      |

|----|--------------|-----|---------|

| Rd | $\leftarrow$ | Rs1 | + Rs2   |

| Rd | $\leftarrow$ | Rs1 | - Rs2   |

| Rd | $\leftarrow$ | Rs1 | And Rs2 |

| Rd | $\leftarrow$ | Rs1 | Or Rs2  |

#### Instruções Formato R, transf de dados

| lw  | Rd,  | Rs1 |

|-----|------|-----|

| SW  | Rs1, | Rs2 |

| in  | Rd   |     |

| out | Rs1  |     |

| Op(3126) | Rd(2521)                      | Rs1(2016)                       | Rs2(1511) | Unused(100)          |

|----------|-------------------------------|---------------------------------|-----------|----------------------|

| 010 111  |                               |                                 | -         | 1                    |

| 010 111  | -                             |                                 |           | 1                    |

| 100 000  |                               | -                               | -         | -                    |

| 110 000  | -                             |                                 | -         | 1                    |

| 6        | 5                             | 5                               | 5         | 5                    |

|          | 010 111<br>010 111<br>100 000 | 010 111<br>010 111 -<br>100 000 | 010 111   | 010 111 -<br>100 000 |

| Obs                     |

|-------------------------|

| $Rd \leftarrow DM(Rs1)$ |

| DM(Rs1) ← Rs2           |

| Rd ← IO_data_in         |

| IO_data_out ← Rs1       |

#### Instruções Formato J, desvio

| J  | addr |  |

|----|------|--|

| Ві | cΖ   |  |

| Ві | ſN   |  |

| Ві | CV   |  |

| Ві | cC   |  |

| Ві | cnZ  |  |

| Ві | cnN  |  |

| Ві | cnV  |  |

| Op(3126) | Addr(250) |

|----------|-----------|

| 111 111  |           |

| 111 000  |           |

| 111 001  |           |

| 111 010  |           |

| 111 011  |           |

| 111 100  |           |

| 111 101  |           |

| 111 110  |           |

|      | Obs               |  |

|------|-------------------|--|

| Pc ∢ | <pre>– addr</pre> |  |

| 11   | if Z=1            |  |

| 11   | if N=1            |  |

| 11   | if V=1            |  |

| 11   | if C=1            |  |

| 11   | if Z=0            |  |

| 11   | if N=0            |  |

| 17   | if V=0            |  |

Ohs

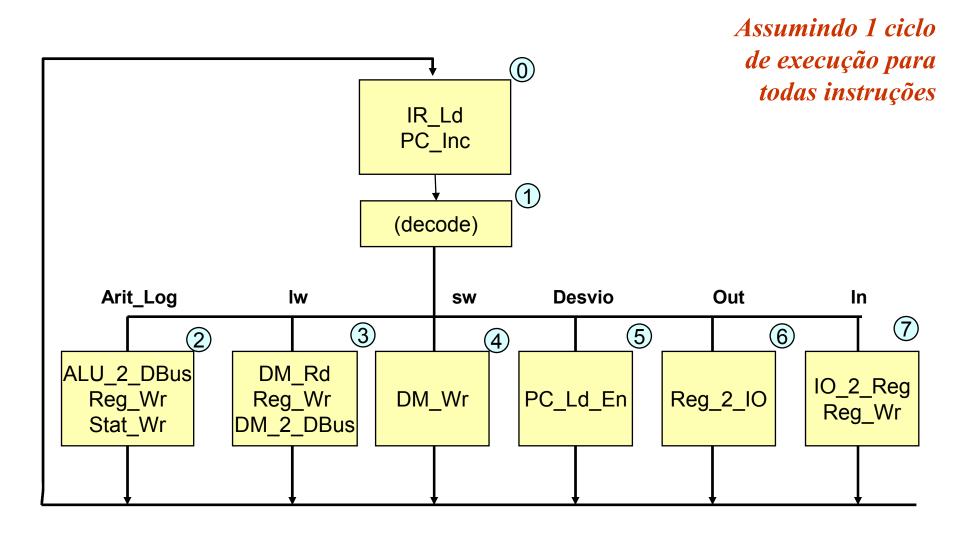

## Ciclos de execução: Fetch e Decode

- Ciclo 1: Fetch (busca de instrução)

- IR\_Ld: saída da IM escrita em IR

- saída de IM mostra continuamente conteúdo da posição apontada por PC

- PC\_Inc: atualiza PC

- a ser usado na próxima instrução

- pode ser sobre-escrito se instrução = desvio

- Ciclo 2: Decodificação

- Um ciclo para a unidade de controle decodificar a instrução e gerar os sinais de controle

Ciclo 3 de execução: arit/lógicas

Rs2

Rs1

- Configura ALU

- função: ALU\_OP

- operandos de entrada: Rs1, Rs2

- registrador de destino: Rd

- ALU 2 DBus

- Ao final do ciclo (borda do próx. clock), escrita

- No registrador de destino: Reg\_Wr

- No registrador de status: Stat\_Wr

- Pode ser realizada em um ciclo ou 2

- caminho crítico: seleciona operandos, envia p ALU, realiza operação (32bits), aciona barramento, escreve em Rd

# Ciclo 3 de execução: lw e sw

- DM no ciclo 2, definidos

- Endereço: Rs1

- Dados para escrita: Rs2

- Registrador destino: Rd

- SW

- DM (Rs1) ← Rs2

- ao final do ciclo: DM Wr

- lw

- Rd ← DM (Rs1)

- DM\_2\_DBus = 1

- ao final do ciclo: Reg\_Wr

- Pode ser realizada em um ciclo ou 2

- caminho crítico: seleciona dados e endereço, envia p DM,

operação de leitura ou escrita, aciona barramento, escreve em Rd

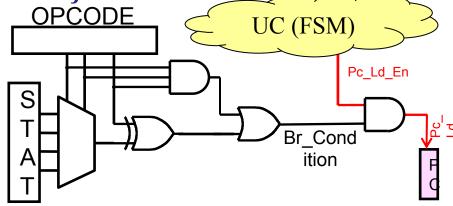

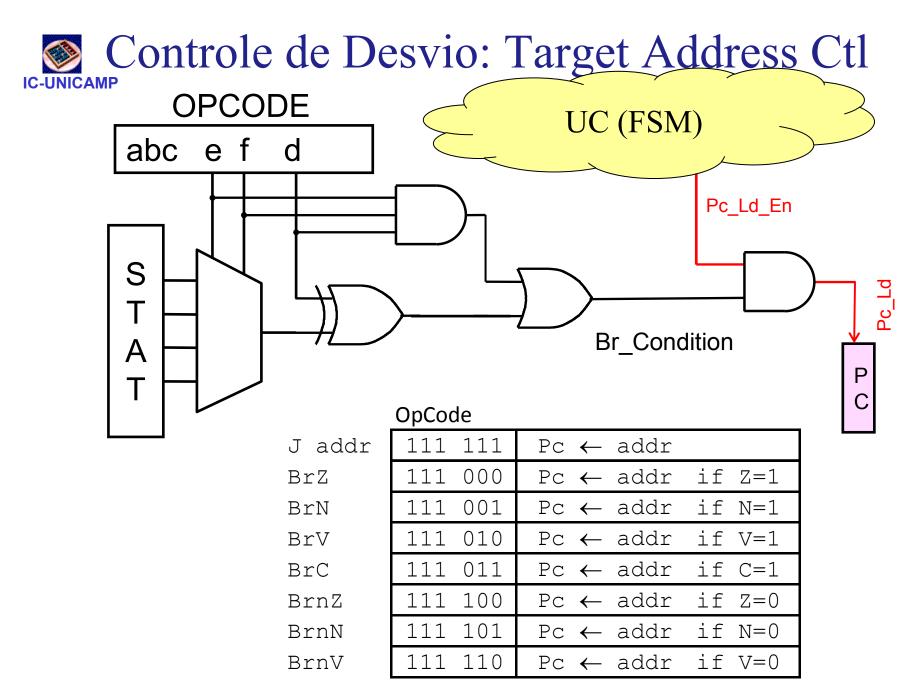

Ciclo 3 de execução: desvio

- Uma única ação da UC

- ver

- sinalizar momento dacarga de PC → Pc\_Ld\_En

- Desvio condicional

- opcode comparado com condição em STAT (última operação aritmética)

- Desvio incondicional

- decodifica OpCode e gera condição, independente de STAT

# Ciclo 3 de execução: I/O

- In Rd

- Rd ← I/O

- controles: IO\_2\_Reg

- ao final do clock: Reg\_Wr

- Out Rs1

- I/O ← Rs1

- controles: Reg\_2\_IO

- Pode ser realizada em um ciclo ou 2

- caminho crítico: seleciona Rd, ativa leitura do barramento, escreve em Rd

## Controle de Desvio: Possibilidades

- Um estado para cada instrução de desvio

- Teste é específico para o estado

- Haverá tantos estados específicos quanto instruções de desvio

- Complica a máquina de estados desnecessáriamente

### Alternativa

- Um único estado na FSM de controle sinaliza instrução de desvio

- Hardware especializado para controlar desvios (Target Address Controller – TrgtAdrCtl)

- Situado entre a FSM, PC e Stat

- Menos HW e mais flexibilidade

## Possível fluxo de controle

## Detalhes da UC

FSM + controladores especializados: ALU e PC

# Convenções de timing

- Controles:

- síncronos com clock (mudança na borda de subida +  $\Delta$ )

- Escrita em registradores:

- na próxima borda de subida (sensível à borda)

- Escrita na Data Memory

- depende da implementação da memória

## Conclusão

- Processador usa módulos básicos vistos em circuitos lógicos

- banco de registradores

- barramentos

- ULA

- unidade de controle (FSM)

- memórias

- Detalhes de implementação: MC722

- Detalhes de linguagens de montagem: MC404