## Laboratório 2

1. Observe a seguinte expressão lógica:

$$F(A,B,C,D,E) = \sum (0, 2, 5, 8, 13, 15, 18, 21, 24, 29, 31)$$

- (a) Minimize esta expressão lógica utilizando mapa de Karnaugh

- (b) Escreva a tabela verdade para a expressão;

- (c) Faça o diagrama lógico para a expressão minimizada;

- (d) Implemente este circuito em esquemático (extensão .bdf)

- (e) Implemente este circuito em VHDL estrutural (extensão .vhd)

- (f) Faça a simulação no Quartus para verificar o funcionamento para todas as 32 combinações de entrada dos itens (d) e (e).

- (g) Teste estes circuitos na DE1 (use as chaves *dip switch* como entrada e um led como saída).

- (h) Verifique os netlists gerados pelo Quartus para ambas as versões, bdf e vhd.

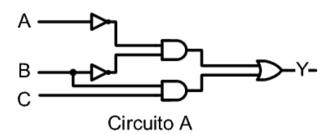

- 2. Considere o circuito apresentado em aula para ilustrar a ocorrência de hazards:

- (a) Implementar o circuito na DE1 (em bdf)

- (b) Faça a simulação funcional do circuito

- (c) Faça a simulação de timing para o circuito. Explique o que acontece. Isto difere do comportamento esperado quanto a hazards?

- (d) Qual seria a possível explicação?