# **Chapter 38 General Purpose Timer (GPT)**

#### 38.1 Overview

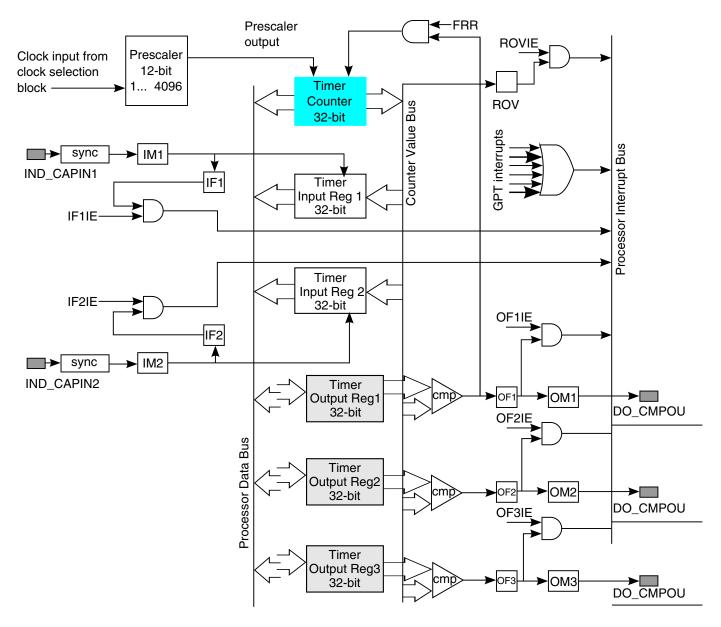

The General Purpose Timer (GPT) has a 32-bit up-counter. The timer counter value can be captured in a register using an event on an external pin. The capture trigger can be programmed to be a rising or/and falling edge. The GPT can also generate an event on the DO\_CMPOUT*n* pins and an interrupt when the timer reaches a programmed value. The GPT has a 12-bit prescaler, which provides a programmable clock frequency derived from multiple clock sources.

Figure 38-1. GPT Block Diagram

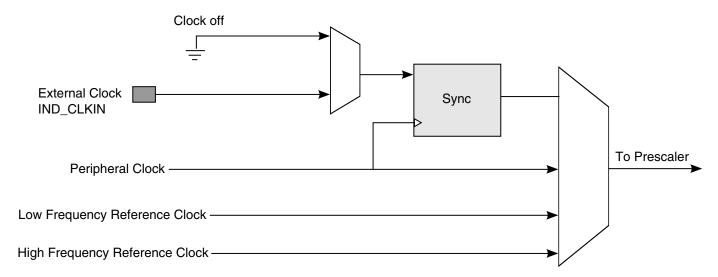

Figure 38-2 shows the GPT functional clocking scheme.

Figure 38-2. GPT Counter Clocks Diagram

#### **38.1.1 Features**

- One 32-bit up-counter with clock source selection, including external clock.

- Two input capture channels with a programmable trigger edge.

- Three output compare channels with a programmable output mode. A "forced compare" feature is also available.

- Can be programmed to be *active* in low power and debug modes.

- Interrupt generation at capture, compare, and rollover events.

- Restart or free-run modes for counter operations.

## 38.1.2 Modes and Operation

The GPT supports the modes described in the indicated sections:

- Operating Modes

- Restart Mode

- Free-Run Mode

## 38.2 External Signals

Table 38-1. Module Signal Conventions

| Category                                  | Convention                                                                     | Example(s)             |

|-------------------------------------------|--------------------------------------------------------------------------------|------------------------|

| Off-chip signal                           | Uppercase (all capital letters)                                                | TXD                    |

| Internal signal <sup>1</sup>              | Lowercase italics                                                              | core_int               |

| Active low signal                         | _B (_b) suffix or overbar                                                      | RESET_EN_B or RESET_EN |

| Range of bussed or commonly named         | Beginning and end points of the range are:                                     | ADDR[31:0]             |

| signals                                   | <ul><li>Separated by a colon.</li><li>Surrounded by square brackets.</li></ul> | CSE_B[7:0] or CSE[7:0] |

| Individual signal in a range of bussed or | Individual number in the range appears                                         | ADDR31                 |

| commonly named signals                    | without a colon or square brackets                                             | CSE0_B or CSE0         |

<sup>1.</sup> Internal signals are for reference only in descriptions of internal module or SoC functionality.

The GPT follows the IP Bus protocol for interfacing with the processor core. The GPT does not have *any interface signals with any other module inside the chip*, except for the clock and reset inputs (from the clock and reset controller module) and for the interrupt signals *to* the processor interrupt handler. There are functional and clock inputs, and functional output signals going outside the chip boundary.

The following table describes all block signals that connect off-chip.

Table 38-2.

Off-Chip Module Signals

| Name       | Direction | Function                                                                            | Reset<br>State | Pull-Up               |

|------------|-----------|-------------------------------------------------------------------------------------|----------------|-----------------------|

| IND_CLKIN  | I         | Input pin for an external clock that the counter can be operated at.                | -              | Passive<br>Hysteresis |

| IND_CAPIN1 | I         | Input pin for a capture event for Input Capture Channel 1.                          | -              | Passive               |

| IND_CAPIN2 | I         | Input pin for a capture event for Input Capture Channel 2.                          | -              | Passive               |

| DO_CMPOUT1 | 0         | Output pin that indicates a "compare event" occurrence in Output Compare Channel 1. | 0              | Passive               |

| DO_CMPOUT2 | 0         | Output pin that indicates a "compare event" occurrence in Output Compare Channel 2. | 0              | Passive               |

| DO_CMPOUT3 | 0         | Output pin that indicates a "compare event" occurrence in Output Compare Channel 3. | 0              | Passive               |

There are six signals (three input, three output) in the GPT module that *can be* connected to the chip pads.

## 38.2.1 External Clock Input: IND\_CLKIN

The GPT counter can be operated using an external clock from outside the device, and this is the input pin used for that purpose. This clock is treated as asynchronous to the peripheral clock. To ensure proper operations of GPT, the external clock input frequency should be less than 1/4 of frequency of the peripheral clock. Hysteresis characteristics on this pad will be required because this is a clock input.

## 38.2.2 Input Capture Trigger Signals: IND\_CAPIN1, IND\_CAPIN2

The GPT counter value can be stored in a register, triggered by an event from *outside the device*. A positive or/and negative edge on these signals can trigger this capture event. These signals are treated as asynchronous to the peripheral clock. Only those transitions which occur *at least a single clock cycle* (the clock selected to run the counter) *after the previous recorded transition* are guaranteed to trigger a capture event.

## 38.2.3 Output Compare Signals: DO\_CMPOUT1, DO\_CMPOUT2, DO\_CMPOUT3

The output compare signals indicate that output compare events have gone through a specified transition.

## 38.3 Programmable Registers

The GPT has 10 user-accessible 32-bit registers, which are used to configure, operate, and monitor the state of the GPT.

An IP bus write access to the GPT Control Register (GPT\_CR) and the GPT Output Compare Register1 (GPT\_OCR1) results in *one cycle of wait state*, while other valid IP bus accesses incur 0 wait states.

Irrespective of the Response Select signal value, a Write access to the GPT Status Registers (Read-only registers GPT\_ICR1, GPT\_ICR2, GPT\_CNT) will generate a bus exception.

#### **Programmable Registers**

- If the Response Select signal is driven Low, then the Read/Write access to the *unimplemented* address space of GPT (*ips\_addr* is greater than or equal to \$BASE + \$028) will generate a bus exception.

- If the Response Select is driven High, then the Read/Write access to the unimplemented address space of GPT will *not* generate any error response (like a bus exception).

#### **GPT** memory map

| Absolute<br>address<br>(hex) | Register name                            | Width<br>(in bits) | Access | Reset value    | Section/<br>page |

|------------------------------|------------------------------------------|--------------------|--------|----------------|------------------|

| 53FA_0000                    | GPT Control Register (GPT_CR)            | 32                 | R/W    | 0000_0000h     | 38.3.1/<br>1741  |

| 53FA_0004                    | GPT Prescaler Register (GPT_PR)          | 32                 | R/W    | 0000_0000h     | 38.3.2/<br>1744  |

| 53FA_0008                    | GPT Status Register (GPT_SR)             | 32                 | R/W    | 0000_0000h     | 38.3.3/<br>1745  |

| 53FA_000C                    | GPT Interrupt Register (GPT_IR)          | 32                 | R/W    | 0000_0000h     | 38.3.4/<br>1746  |

| 53FA_0010                    | GPT Output Compare Register 1 (GPT_OCR1) | 32                 | R/W    | FFFF_<br>FFFFh | 38.3.5/<br>1747  |

| 53FA_0014                    | GPT Output Compare Register 2 (GPT_OCR2) | 32                 | R/W    | FFFF_<br>FFFFh | 38.3.6/<br>1748  |

| 53FA_0018                    | GPT Output Compare Register 3 (GPT_OCR3) | 32                 | R/W    | FFFF_<br>FFFFh | 38.3.7/<br>1748  |

| 53FA_001C                    | GPT Input Capture Register 1 (GPT_ICR1)  | 32                 | R      | 0000_0000h     | 38.3.8/<br>1749  |

| 53FA_0020                    | GPT Input Capture Register 2 (GPT_ICR2)  | 32                 | R      | 0000_0000h     | 38.3.9/<br>1749  |

| 53FA_0024                    | GPT Counter Register (GPT_CNT)           | 32                 | R      | 0000_0000h     | 38.3.10/<br>1750 |

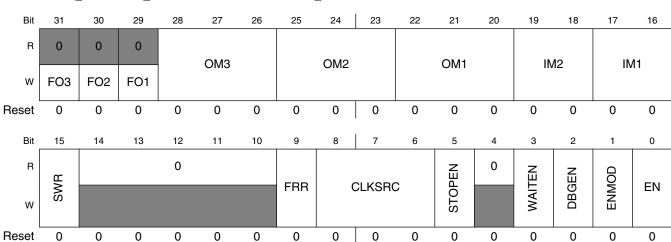

## 38.3.1 GPT Control Register (GPT\_CR)

The GPT Control Register (GPT\_CR) is used to program and configure GPT operations. An IP Bus Write to the GPT Control Register occurs after one cycle of wait state, while an IP Bus Read occurs after 0 wait states.

Address: GPT\_CR is 53FA\_0000h base + 0h offset = 53FA\_0000h

#### **GPT\_CR** field descriptions

| Field     | Description                                                                                                                                          |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31        | FO3 Force Output Compare Channel 3                                                                                                                   |

| FO3       | FO2 Force Output Compare Channel 2                                                                                                                   |

|           | FO1 Force Output Compare Channel 1                                                                                                                   |

|           | The FO $n$ bit causes the pin action <i>programmed</i> for the timer Output Compare $n$ pin (according to the OM $n$ bits in this register).         |

|           | <ul> <li>The OFn flag (OF3, OF2, OF1) in the status register is not affected.</li> <li>This bit is self-negating and always read as zero.</li> </ul> |

|           | 0 Writing a 0 has no effect.                                                                                                                         |

|           | 1 Causes the programmed pin action on the timer Output Compare n pin; the OFn flag is not set.                                                       |

| 30<br>FO2 | See F03                                                                                                                                              |

| 29<br>FO1 | See F03                                                                                                                                              |

| 28–26     | OM3 (bits 28-26) controls the Output Compare Channel 3 operating mode.                                                                               |

| OM3       | OM2 (bits 25-23) controls the Output Compare Channel 2 operating mode.                                                                               |

|           | OM1 (bits 22-20) controls the Output Compare Channel 1 operating mode.                                                                               |

|           | The OMn bits specify the response that a compare event will generate on the output pin of Output Compare Channel n.                                  |

## **GPT\_CR** field descriptions (continued)

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | <ul> <li>The toggle, clear, and set options cause a change on the output pin <i>only</i> if a compare event occurs.</li> <li>When OMn is programmed as 1xx (active low pulse), the output pin is set to one immediately on the next input clock; a low pulse (that is an input clock in width) occurs when there is a compare event. Note that here, "input clock" refers to the clock selected by the CLKSRC bits of the GPT Control Register.</li> </ul> |

|                   | 000 Output disconnected. No response on pin.                                                                                                                                                                                                                                                                                                                                                                                                               |

|                   | 001 Toggle output pin 010 Clear output pin                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | 011 Set output pin                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                   | 1xx Generate an active low pulse (that is one input clock wide) on the output pin.                                                                                                                                                                                                                                                                                                                                                                         |

| 25–23<br>OM2      | See OM3                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 22–20<br>OM1      | See OM3                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 19–18<br>IM2      | IM2 (bits 19-18, Input Capture Channel 2 operating mode)                                                                                                                                                                                                                                                                                                                                                                                                   |

| IIVI∠             | IM1 (bits 17-16, Input Capture Channel 1 operating mode)                                                                                                                                                                                                                                                                                                                                                                                                   |

|                   | The $IMn$ bit field determines the transition on the input pin (for Input capture channel $n$ ), which will trigger a capture event.                                                                                                                                                                                                                                                                                                                       |

|                   | 00 capture disabled                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                   | <ul><li>01 capture on rising edge only</li><li>10 capture on falling edge only</li></ul>                                                                                                                                                                                                                                                                                                                                                                   |

|                   | 11 capture on both edges                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 17–16<br>IM1      | See IM2                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15                | Software reset.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SWR               | This is the software reset of the GPT module. It is a self-clearing bit.                                                                                                                                                                                                                                                                                                                                                                                   |

|                   | <ul> <li>The SWR bit is set when the module is in reset state.</li> <li>The SWR bit is cleared when the reset procedure finishes.</li> </ul>                                                                                                                                                                                                                                                                                                               |

|                   | <ul> <li>Setting the SWR bit resets all of the registers to their default reset values, except for the CLKSRC, EN, ENMOD, STOPEN, WAITEN, and DBGEN bits in the GPT Control Register (this control register).</li> </ul>                                                                                                                                                                                                                                   |

|                   | 0 GPT is not in reset state                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | 1 GPT is in reset state                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14–10<br>Reserved | This read-only bitfield is reserved and always has the value zero.  Reserved bits.                                                                                                                                                                                                                                                                                                                                                                         |

|                   | <ul> <li>Writing a value to these reserved bits will not affect GPT operations.</li> <li>These reserved bits are always read as zero.</li> <li>It is recommended that all writes to these reserved bits be 0 (for forward compatibility).</li> </ul>                                                                                                                                                                                                       |

| 9                 | Free-Run or Restart mode.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| FRR               | The FFR bit determines the behavior of the GPT when a compare event in channel 1 occurs.                                                                                                                                                                                                                                                                                                                                                                   |

|                   | <ul> <li>In Restart mode, after a compare event, the counter resets to 0x00000000 and resumes counting (after the occurrence of a compare event).</li> <li>In Free-Run mode, after a compare event, the counter continues counting until 0xFFFFFFF and then rolls over to 0.</li> </ul>                                                                                                                                                                    |

## **GPT\_CR** field descriptions (continued)

| Field         | Description                                                                                                                                                                                                                              |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | 0 Restart mode                                                                                                                                                                                                                           |

|               | 1 Free-Run mode                                                                                                                                                                                                                          |

| 8–6           | Clock Source select.                                                                                                                                                                                                                     |

| CLKSRC        | The CLKSRC bits select which clock will go to the prescaler (and subsequently be used to run the GPT counter).                                                                                                                           |

|               | <ul> <li>The CLKSRC bit field value should only be changed after disabling the GPT by clearing the EN bit in this register (GPT_CR).</li> <li>A software reset does not affect the CLKSRC bit.</li> </ul>                                |

|               | 000 No clock<br>001 Peripheral Clock                                                                                                                                                                                                     |

|               | 010 High Frequency Reference Clock                                                                                                                                                                                                       |

|               | 011 External Clock (IND_CLKIN)                                                                                                                                                                                                           |

|               | 1xx Low Frequency Reference Clock                                                                                                                                                                                                        |

| 5             | GPT Stop Mode enable.                                                                                                                                                                                                                    |

| STOPEN        | The STOPEN read/write control bit enables GPT operation during Stop mode.                                                                                                                                                                |

|               | <ul> <li>A hardware reset resets the STOPEN bit.</li> <li>A software reset does not affect the STOPEN bit.</li> </ul>                                                                                                                    |

|               | 0 GPT is disabled in Stop mode.                                                                                                                                                                                                          |

|               | 1 GPT is enabled in Stop mode.                                                                                                                                                                                                           |

| 4<br>Reserved | This read-only bit is reserved and always has the value zero.  Reserved bit.  Writing a value to this reserved bit will not affect GPT operations.                                                                                       |

|               | Reading this bit will return the last written value.                                                                                                                                                                                     |

| 3<br>WAITEN   | GPT Wait Mode enable.                                                                                                                                                                                                                    |

|               | The WAITEN read/write control bit enables GPT operation during Wait mode.                                                                                                                                                                |

|               | <ul> <li>A hardware reset resets the WAITEN bit.</li> <li>A software reset does not affect the WAITEN bit.</li> </ul>                                                                                                                    |

|               | 0 GPT is disabled in wait mode.                                                                                                                                                                                                          |

|               | 1 GPT is enabled in wait mode.                                                                                                                                                                                                           |

| 2             | GPT debug mode enable.                                                                                                                                                                                                                   |

| DBGEN         | The DBGEN read/write control bit enables GPT operation during Debug mode.                                                                                                                                                                |

|               | <ul> <li>A hardware reset resets the DBGEN bit.</li> <li>A software reset does not affect the DBGEN bit.</li> </ul>                                                                                                                      |

|               | <ul><li>0 GPT is disabled in debug mode.</li><li>1 GPT is enabled in debug mode.</li></ul>                                                                                                                                               |

| 1             | GPT Enable mode.                                                                                                                                                                                                                         |

| ENMOD         | When the GPT is disabled (EN=0), then both the Main Counter and Prescaler Counter <i>freeze their current count values</i> . The ENMOD bit determines the value of the GPT counter when Counter is enabled again (if the EN bit is set). |

## **GPT\_CR field descriptions (continued)**

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>If the ENMOD bit is 1, then the Main Counter and Prescaler Counter values are reset to 0 after GPT is enabled (EN=1).</li> <li>If the ENMOD bit is 0, then the Main Counter and Prescaler Counter restart counting from their frozen values after GPT is enabled (EN=1).</li> </ul>                                                                                                                                                                                                                 |

|       | <ul> <li>If GPT is programmed to be disabled in a low power mode (STOP/WAIT), then the Main Counter and Prescaler Counter freeze at their current count values when the GPT enters low power mode.</li> <li>When GPT exits low power mode, the Main Counter and Prescaler Counter start counting from their frozen values, regardless of the ENMOD bit value.</li> <li>Setting the SWR bit will clear the Main Counter and Prescaler Counter values, regardless of the value of EN or ENMOD bits.</li> </ul> |

|       | <ul> <li>A hardware reset resets the ENMOD bit.</li> <li>A software reset does not affect the ENMOD bit.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 0 GPT counter will retain its value when it is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | 1 GPT counter value is reset to 0 when it is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0     | GPT Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| EN    | The EN bit is the GPT module enable bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | Before setting the EN bit, we recommend that all registers be properly programmed.                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | <ul> <li>A hardware reset resets the EN bit.</li> <li>A software reset does not affect the EN bit.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                |

|       | <ul><li>0 GPT is disabled.</li><li>1 GPT is enabled.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                               |

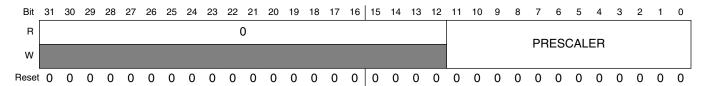

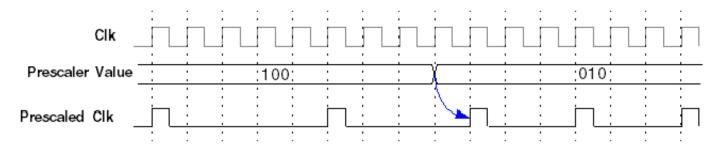

## 38.3.2 GPT Prescaler Register (GPT\_PR)

The GPT Prescaler Register (GPT\_PR) contains bits that determine the divide value of the clock that runs the counter.

Address: GPT\_PR is 53FA\_0000h base + 4h offset = 53FA\_0004h

#### **GPT\_PR** field descriptions

| Field             | Description                                                                                                                                                                                                  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–12<br>Reserved | This read-only bitfield is reserved and always has the value zero.  Reserved bits.  • Writing a value to these reserved bits will not affect GPT operations.  • These reserved bits are always read as zero. |

## **GPT\_PR field descriptions (continued)**

| Field     | Description                                                                                                                                                                                         |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11–0      | Prescaler bits.                                                                                                                                                                                     |

| PRESCALER | The clock selected by the CLKSRC field is divided by [PRESCALER + 1], and then used to run the counter.                                                                                             |

|           | <ul> <li>A change in the value of the PRESCALER bits cause the Prescaler counter to reset and a new count period to start immediately.</li> <li>See Figure 38-13 for the timing diagram.</li> </ul> |

|           | 0x000 Divide by 1                                                                                                                                                                                   |

|           | 0x001 Divide by 2                                                                                                                                                                                   |

|           | 0xFFF Divide by 4096                                                                                                                                                                                |

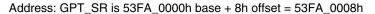

## 38.3.3 GPT Status Register (GPT\_SR)

The GPT Status Register (GPT\_SR) contains bits that indicate that a counter has rolled over, and if any event has occurred on the Input Capture and Output Compare channels. The bits are cleared by writing a 1 to them.

#### **GPT\_SR** field descriptions

| Field            | Description                                                                                                                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–6<br>Reserved | This read-only bitfield is reserved and always has the value zero.  Reserved bits.                                                                                                                                                                                             |

| 1.000.100        | <ul> <li>Writing a value to these reserved bits will not affect GPT operations.</li> <li>These reserved bits are always read as zero.</li> </ul>                                                                                                                               |

| 5<br>ROV         | Rollover Flag.  The ROV bit indicates that the counter has reached its <i>maximum possible value</i> and <i>rolled over</i> to 0 (from which the counter continues counting). The ROV bit is only set if the counter has reached 0xFFFFFFF in both Restart and Free-Run modes. |

#### **GPT\_SR** field descriptions (continued)

| Field    | Description                                                                                                                                                                                                                      |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Rollover has not occurred.     Rollover has occurred.                                                                                                                                                                            |

| 4<br>IF2 | IF2 Input capture 2 Flag IF1 Input capture 1 Flag The IFn bit indicates that a capture event has occurred on Input Capture channel n.  Capture event has not occurred.  Capture event has occurred.                              |

| 3<br>IF1 | See IF2                                                                                                                                                                                                                          |

| 2<br>OF3 | OF3 Output Compare 3 Flag OF2 Output Compare 2 Flag OF1 Output Compare 1 Flag The OFn bit indicates that a compare event has occurred on Output Compare channel n.  Compare event has not occurred.  Compare event has occurred. |

| 1<br>OF2 | See OF3                                                                                                                                                                                                                          |

| 0<br>OF1 | See OF3                                                                                                                                                                                                                          |

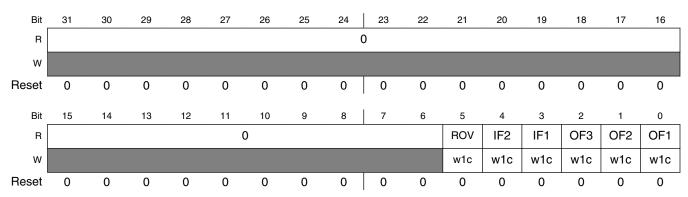

## 38.3.4 GPT Interrupt Register (GPT\_IR)

The GPT Interrupt Register (GPT\_IR) contains bits that control whether interrupts are generated after rollover, input capture and output compare events.

Address: GPT\_IR is 53FA\_0000h base + Ch offset = 53FA\_000Ch

#### **GPT\_IR** field descriptions

| Field            | Description                                                                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–6<br>Reserved | This read-only bitfield is reserved and always has the value zero.  Reserved bits.  • Writing a value to these reserved bits will not affect GPT operations.  • These reserved bits are always read as zero. |

#### **GPT\_IR** field descriptions (continued)

| Field      | Description                                                        |

|------------|--------------------------------------------------------------------|

| 5          | Rollover Interrupt Enable.                                         |

| ROVIE      | The ROVIE bit controls the Rollover interrupt.                     |

|            | 0 Rollover interrupt is disabled.                                  |

|            | 1 Rollover interrupt enabled.                                      |

| 4          | IF2IE Input capture 2 Interrupt Enable                             |

| IF2IE      | IF1IE Input capture 1 Interrupt Enable                             |

|            | The IFnIE bit controls the IFnIE Input Capture n Interrupt Enable. |

|            | 0 IF2IE Input Capture n Interrupt Enable is disabled.              |

|            | 1 IF2IE Input Capture n Interrupt Enable is enabled.               |

| 3<br>IF1IE | See IF2IE                                                          |

| 2          | OF3IE Output Compare 3 Interrupt Enable                            |

| OF3IE      | OF2IE Output Compare 2 Interrupt Enable                            |

|            | OF1IE Output Compare 1 Interrupt Enable                            |

|            | The OFnIE bit controls the Output Compare Channel n interrupt.     |

|            | 0 Output Compare Channel n interrupt is disabled.                  |

|            | 1 Output Compare Channel n interrupt is enabled.                   |

| 1<br>OF2IE | See OF3IE                                                          |

| 0<br>OF1IE | See OF3IE                                                          |

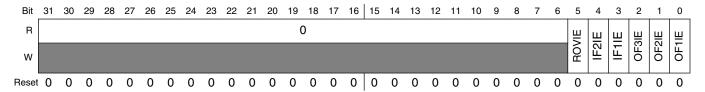

## 38.3.5 GPT Output Compare Register 1 (GPT\_OCR1)

The GPT Compare Register 1 (GPT\_OCR1) holds the value that determines when a compare event will be generated on Output Compare Channel 1. Any write access to the Compare register of Channel 1 while in Restart mode (FRR=0) will reset the GPT counter.

An IP Bus Write access to the GPT Output Compare Register1 (GPT\_OCR1) occurs *after* one cycle of wait state; an IP Bus Read access occurs *immediately* (0 wait states).

Address: GPT\_OCR1 is 53FA\_0000h base + 10h offset = 53FA\_0010h

#### **GPT\_OCR1** field descriptions

| Field | Description                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| COMP  | Compare Value.  When the counter value equals the COMP bit field value, a compare event is generated on Output Compare Channel 1. |

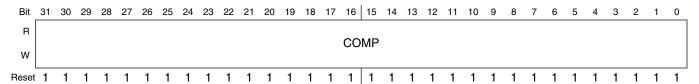

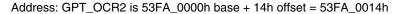

## 38.3.6 GPT Output Compare Register 2 (GPT\_OCR2)

The GPT Compare Register 2 (GPT\_OCR2) holds the value that determines when a compare event will be generated on Output Compare Channel 2.

#### **GPT\_OCR2** field descriptions

| Field        | Description                                                                                                                       |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 31–0<br>COMP | Compare Value.  When the counter value equals the COMP bit field value, a compare event is generated on Output Compare Channel 2. |

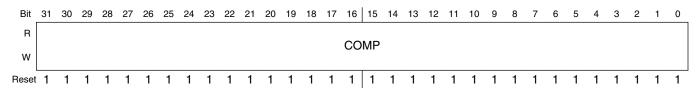

## 38.3.7 GPT Output Compare Register 3 (GPT\_OCR3)

The GPT Compare Register 3 (GPT\_OCR3) holds the value that determines when a compare event will be generated on Output Compare Channel 3.

Address: GPT\_OCR3 is 53FA\_0000h base + 18h offset = 53FA\_0018h

#### **GPT\_OCR3** field descriptions

| Field        | Description                                                                                                                       |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 31–0<br>COMP | Compare Value.  When the counter value equals the COMP bit field value, a compare event is generated on Output Compare Channel 3. |

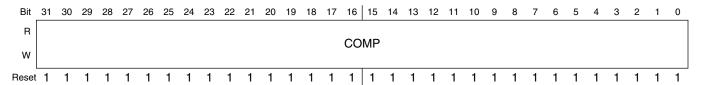

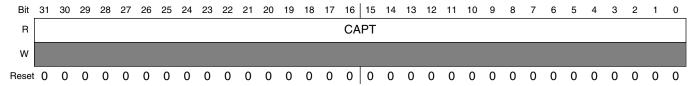

## 38.3.8 GPT Input Capture Register 1 (GPT\_ICR1)

The GPT Input Capture Register 1 (GPT\_ICR1) is a read-only register that holds the value that was in the counter during the last capture event on Input Capture Channel 1.

Address: GPT\_ICR1 is 53FA\_0000h base + 1Ch offset = 53FA\_001Ch

#### **GPT\_ICR1** field descriptions

| Field        | Description                                                                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–0<br>CAPT | Capture Value.  After a capture event on Input Capture Channel 1 occurs, the current value of the counter is loaded into GPT Input Capture Register 1. |

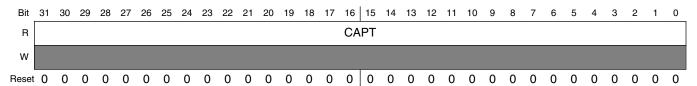

## 38.3.9 GPT Input Capture Register 2 (GPT\_ICR2)

The GPT Input capture Register 2 (GPT\_ICR2) is a read-only register which holds the value that was in the counter during the last capture event on input capture channel 2.

Address: GPT\_ICR2 is 53FA\_0000h base + 20h offset = 53FA\_0020h

#### **GPT\_ICR2** field descriptions

| Field        | Description                                                                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–0<br>CAPT | Capture Value.  After a capture event on Input Capture Channel 2 occurs, the current value of the counter is loaded into GPT Input Capture Register 2. |

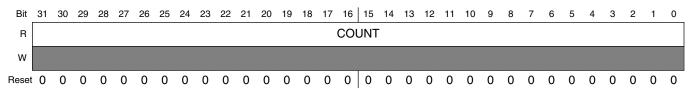

## 38.3.10 GPT Counter Register (GPT\_CNT)

The GPT Counter Register (GPT\_CNT) is the main counter's register. GPT\_CNT is a read-only register and can be read without affecting the counting process of the GPT.

Address: GPT\_CNT is 53FA\_0000h base + 24h offset = 53FA\_0024h

#### **GPT\_CNT** field descriptions

| Field | Description                                                     |

|-------|-----------------------------------------------------------------|

| 31–0  | Counter Value.                                                  |

| COUNT | The COUNT bits show the current count value of the GPT counter. |

## 38.4 Functional Description

This section provides a complete functional description of the GPT.

## 38.4.1 Operating Modes

The GPT counter can be programmed to work in either of two modes: Restart mode or Free-Run mode.

## 38.4.1.1 Restart Mode

In Restart mode (selectable through the GPT Control Register GPT\_CR), when the counter reaches the compared value, the counter resets and starts again from 0x00000000. The Restart feature is associated only with Compare Channel 1.

Any write access to the Compare register of Channel 1 will reset the GPT counter. This is done to avoid possibly missing a compare event when compare value is changed from a higher value to lower value while counting is proceeding.

For the other two compare channels, when the compare event occurs the counter is *not reset*.

#### 38.4.1.2 Free-Run Mode

In Free-Run mode, when compare events occur for all 3 channels, the counter is *not reset*; instead the counter continues to count until 0xffffffff, and then rolls over (to 0x00000000).

## 38.4.2 Operation

The General Purpose Timer (GPT) has a single counter (GPT\_CNT) that is a 32-bit free-running *up-counter*, which starts counting *after it is enabled by software* (EN=1). The counter's clock source is the output of the prescaler labelled "Prescaler output" in Figure 38-1.

- If the GPT timer is disabled (EN=0), then the Main Counter *and* Prescaler Counter freeze their current count values. The ENMOD bit determines the value of the GPT counter when the EN bit is set and the Counter is enabled again.

- If the ENMOD bit is set (=1), then the Main Counter and Prescaler Counter values are reset to 0, when GPT is enabled (EN=1).

- If ENMOD bit is programmed to 0, then the Main Counter and Prescaler Counter restart counting from their frozen values, when GPT is enabled again (EN=1).

- If GPT is programmed to be disabled in a low power mode (STOP/WAIT), then the Main Counter and Prescaler Counter freeze at their current count values *when* GPT enters low power mode. When GPT exits a low power mode, the Main Counter and Prescaler Counter start counting from their frozen values *regardless* of the ENMOD bit value. Note that the GPT\_CNT can be read *at any time* by the processor, and that *both* Input Capture Channels use the *same* counter (GPT\_CNT).

- A hardware reset resets all the GPT registers to their respective reset values. All registers except the Output Compare Registers (OCR1, OCR2, OCR3) obtain a value of 0x0. The Compare registers are reset to 0xffffffff.

- The software reset (SWR bit in the GPT\_CR control register) resets *all* of the register bits *except* the EN, ENMOD, STOPEN, WAITEN, and DBGEN bits. The state of these bits is not affected by a software reset. Note that a software reset can be given *while the GPT is disabled*.

#### 38.4.2.1 Clocks

The clock that is input to the prescaler can be selected from 4 clock sources:

• High Frequency Clock

i.MX53 Multimedia Applications Processor Reference Manual, Rev. 1A, 03/2011

#### **Functional Description**

Provided by the Clock Controller Module (CCM), the High Frequency Clock is intended to be ON in Normal Power mode when the Peripheral Clock is turned OFF, thereby enabling the GPT to be operated using the High Frequency Clock *in Normal Power mode*. The CCM is expected to provide this clock *after* synchronizing it to the System Bus Clock in Normal functional mode; the CCM is also expected to switch to the *unsynchronized* version of the High Frequency Clock in a Low Power mode.

#### Low Reference Clock

This 32 kHz Low Reference Clock (provided by the CCM) is intended to be ON in Low Power mode when the Peripheral Clock is turned OFF, thereby enabling the GPT to be operated using the Low Reference Clock in Low Power mode. The CCM is expected to provide the Low Reference Clock *after* synchronizing it to the System Bus Clock in Normal functional mode; the CCM is also expected to switch to the *unsynchronized* version of the Low Reference Clock in a Low Power mode.

#### External Clock

The External Clock comes from *outside the device* and can be selected to run the GPT counter. The External Clock is treated as *asynchronous to the Peripheral Clock*, and is synchronized to the Peripheral Clock, *inside* the module. Therefore, the External Clock frequency is limited to < 1/4 frequency of the Peripheral Clock, for proper GPT operations. Note that in Low Power modes, *if* the Peripheral Clock is not available, then the External Clock *cannot be used* to run the counter.

## • Peripheral Clock

If the Peripheral Clock or the External Clock is selected(CLKSRC=001 or 011) as Clock Source, then the Peripheral Clock will be ON in normal GPT operations. In Low Power modes, if the GPT is programmed to be disabled (STOPEN or WAITEN or DOZEN=0), then the Peripheral Clock can be switched OFF.

The clock input source is configured using the clock source field (CLKSRC, in the GPT\_CR control register). The clock input to the prescaler can be disabled by programming the CLKSRC bits (of the GPT\_CR control register) to 000. **The CLKSRC field value should be changed** *only after disabling the GPT* (by setting the EN bit in the GPT\_CR to 0).

The PRESCALER field selects the divide ratio of the input clock that drives the main counter. The prescaler can divide the input clock by a value (from 1 to 4096) and can be changed *at any time*. A change in the value of the PRESCALER field *immediately affects* the output clock frequency.

Figure 38-13. Prescaler Value Change Timing Diagram

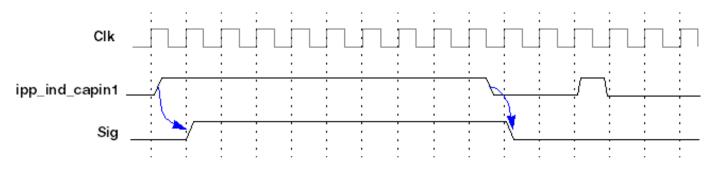

## 38.4.2.2 Input Capture

There are two Input Capture Channels, and each Input Capture Channel has a dedicated capture pin, capture register and input edge detection/selection logic. Each input capture function has an associated status flag, and can cause the processor to make an interrupt service request.

When a selected edge transition occurs on an Input Capture pin, the contents of the GPT\_CNT is captured on the corresponding capture register and the appropriate interrupt status flag is set. An interrupt request can be generated when the transition is detected *if* its corresponding enable bit is set (in the Interrupt Register). The capture can be programmed to occur on the input pin's rising edge, falling edge, on both rising and falling edges, or the capture can be disabled. The events are synchronized with the clock that was selected to run the counter. Only those transitions that occur at least one clock cycle (clock selected to run the counter) *after* the previous recorded transition will be guaranteed to trigger a capture event. There can be up to one clock cycle of uncertainty in the latching of the input transition. The Input Capture registers can be read *at any time* without affecting their values.

Clk — The clock selected from CLKSRC bit field setting ipp\_ind\_capin1 — Pad signal for capture channel 1 Sig — Capture signal as sensed by the module

Figure 38-14. Input Capture Event Timing

i.MX53 Multimedia Applications Processor Reference Manual, Rev. 1A, 03/2011

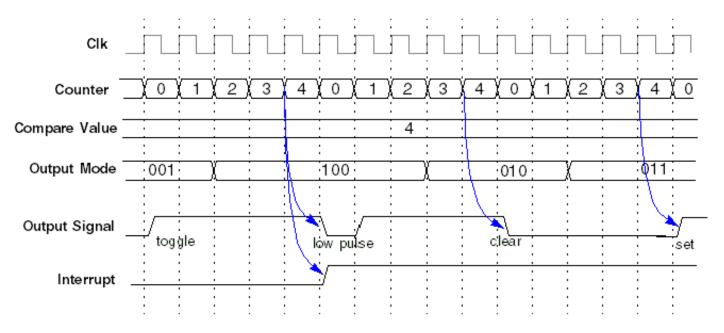

## 38.4.2.3 Output Compare

The three Output Compare Channels *use the same counter* (GPT\_CNT) as the Input Capture Channels. When the programmed content of an Output Compare register matches the value in GPT\_CNT, an output compare status flag is set and an interrupt is generated (if the corresponding bit is set in the interrupt register). Consequently, the Output Compare timer pin will be set, cleared, toggled, not affected at all or provide an active-low pulse for one input clock period (subject to the restriction on the maximum frequency allowed on the pad) according to the mode bits (that were programmed).

There is also a "forced-compare" feature that allows the software to generate a compare event when required, without the condition of the counter value that is equal to the compare value. The action taken as a result of a forced compare is the same as when an output compare match occurs, except that the status flags are not set and no interrupt can be generated. Forced channels take programmed action immediately after the write to the force-compare bits. These bits are self-negating and always read as zeros.

Figure 38-15. Output Compare and Interrupt Timing

## **38.4.2.4** Interrupts

There are 6 different interrupts that are generated by the GPT. If the selected clock for running the counter is available, then *all interrupts can be generated in Low Power and Debug modes*.

• Rollover Interrupt

The Rollover Interrupt is generated when the GPT counter reaches 0xffffffff, then resets to 0x00000000 and continues counting. The Rollover Interrupt is enabled by the ROVIE bit in the GPT\_IR register; the associated status bit is the ROV bit in the GPT\_SR register.

#### • Input Capture Interrupt 1, 2

After a capture event occurs, the associated Input Capture Channel generates an interrupt. The "capture event" interrupts are enabled by the IF2IE and IF1IE bits (in the GPT\_IR register); the associated status bits are IF2 and IF1 (in the GPT\_SR register). The capture of the counter value because of a capture event is *not affected by a pending capture interrupt*. The Capture register is updated with a new counter value when a capture event occurs, regardless of whether that Capture Channels' interrupt has been serviced or not.

#### • Output Compare Interrupt 1, 2, 3

After a compare event occurs, the associated Output Compare Channel generates an interrupt. The "compare event" interrupts are enabled by the OF3IE, OF2IE, and OF1IE bits (in the GPT\_IR register); the associated status bits are OF3, OF2, and OF1 (in the GPT\_SR register). A "forced compare" does not generate an interrupt.

A *cumulative* interrupt line is also present, which is asserted whenever any of the above interrupts are posted. The cumulative interrupt line has *no* associated enables or status bits.

#### 38.4.2.5 Low Power Mode Behavior

In Low Power modes, if the clock from the selected clock source is available (except for the External Clock, which can be used *only if* the Peripheral Clock is available), the counter will continue to run depending on whether the control bit for that mode is set. If the clock is not present or if the corresponding low power bit in the GPT\_CR control register is 0, the Main Counter and the Prescaler Counter freeze at their current values and resume counting (from their frozen values) when the Low Power mode is exited.

## 38.4.2.6 Debug Mode Behavior

In Debug mode, the modules in the device have the option of continuing to run or be halted.

#### **Functional Description**

- If the DBGEN bit is set, then the GPT timer will continue to run in Debug mode.

- If the DBGEN bit is not set (in the GPT\_CR control register), then the GPT timer is halted.