### Instruction Execution

- PC → instruction memory, fetch instruction

- Register numbers → register file, read registers

- Depending on instruction class

- Use ALU to calculate

- Arithmetic result

- Memory address for load/store

- Branch target address

- Access data memory for load/store

- PC ← target address or PC + 4

Chapter 4 — The Processor — 3

### Performance Issues

- Longest delay determines clock period

- Critical path: load instruction

- Instruction memory  $\rightarrow$  register file  $\rightarrow$  ALU  $\rightarrow$  data memory  $\rightarrow$  register file

- Not feasible to vary period for different instructions

- Violates design principle

- Making the common case fast

- We will improve performance by pipelining

Chapter 4 — The Processor — 30

# Pipelining Analogy Pipelined laundry: overlapping execution ■ Parallelism improves performance Four loads: ■ Speedup = 8/3.5 = 2.3 Non-stop: ■ Speedup = 2n/0.5n + 1.5 ≈ 4 = number of stages

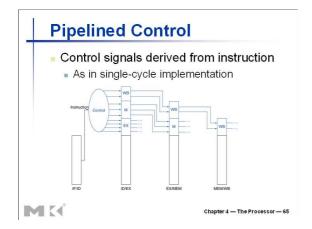

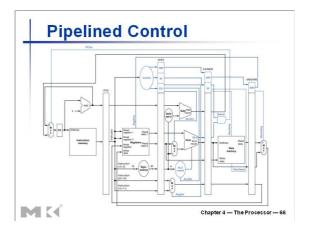

### **MIPS Pipeline**

- Five stages, one step per stage

- 1. IF: Instruction fetch from memory

- 2. ID: Instruction decode & register read

- 3. EX: Execute operation or calculate address

- 4. MEM: Access memory operand

- 5. WB: Write result back to register

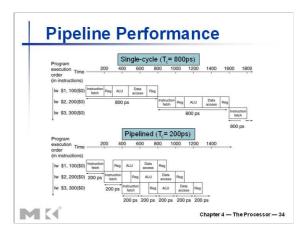

# **Pipeline Performance**

- Assume time for stages is

- 100ps for register read or write

- 200ps for other stages

- Compare pipelined datapath with single-cycle datapath

| Instr    | Instr fetch | Register<br>read | ALU op | Memory<br>access | Register<br>write | Total time |

|----------|-------------|------------------|--------|------------------|-------------------|------------|

| lw       | 200ps       | 100 ps           | 200ps  | 200ps            | 100 ps            | 800ps      |

| sw       | 200ps       | 100 ps           | 200ps  | 200ps            |                   | 700ps      |

| R-format | 200ps       | 100 ps           | 200ps  |                  | 100 ps            | 600ps      |

| beq      | 200ps       | 100 ps           | 200ps  |                  |                   | 500ps      |

Chapter 4 — The Processor — 33

### **Pipeline Speedup**

- If all stages are balanced

- . i.e., all take the same time

- Time between instructions<sub>pipelined</sub>

- = Time between instructions $_{nonpipelined}$ Number of stages

- If not balanced, speedup is less

- Speedup due to increased throughput

- Latency (time for each instruction) does not decrease

Chapter 4 — The Processor — 35

# **Pipelining and ISA Design**

- MIPS ISA designed for pipelining

- All instructions are 32-bits

- Easier to fetch and decode in one cycle

- c.f. x86: 1- to 17-byte instructions

- Few and regular instruction formats

- Can decode and read registers in one step

- Load/store addressing

- Can calculate address in 3rd stage, access memory

- Alignment of memory operands

- Memory access takes only one cycle

Chapter 4 — The Processor — 36

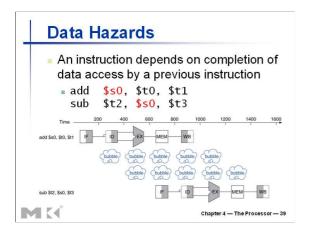

### **Hazards**

- Situations that prevent starting the next instruction in the next cycle

- Structure hazards

- A required resource is busy

- - Need to wait for previous instruction to complete its data read/write

- Control hazard

- Deciding on control action depends on previous instruction

Chapter 4 — The Processor — 37

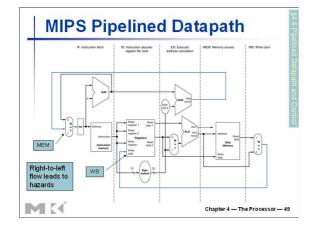

### Structure Hazards

- Conflict for use of a resource

- In MIPS pipeline with a single memory

- Load/store requires data access

- Instruction fetch would have to stall for that cycle

- Would cause a pipeline "bubble"

- Hence, pipelined datapaths require separate instruction/data memories

- Or separate instruction/data caches

MK

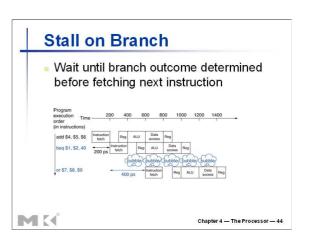

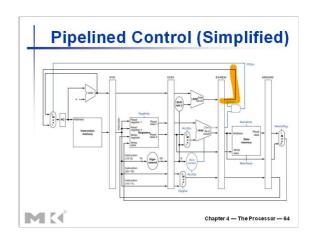

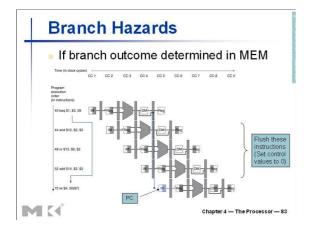

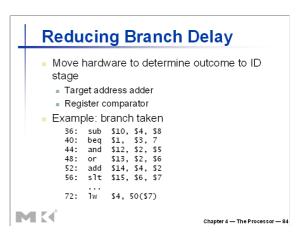

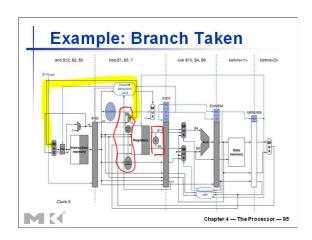

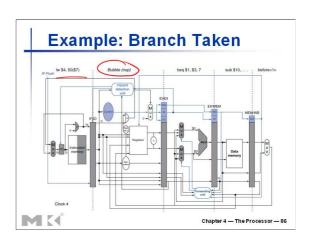

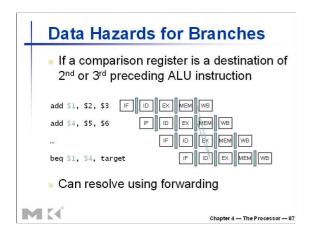

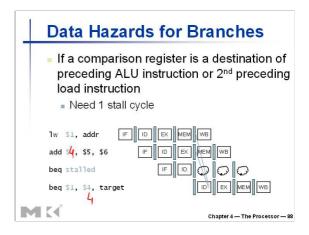

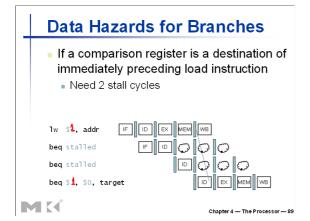

# Control Hazards Branch determines flow of control Fetching next instruction depends on branch outcome Pipeline can't always fetch correct instruction Still working on ID stage of branch In MIPS pipeline Need to compare registers and compute target early in the pipeline Add hardware to do it in ID stage

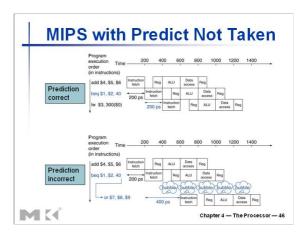

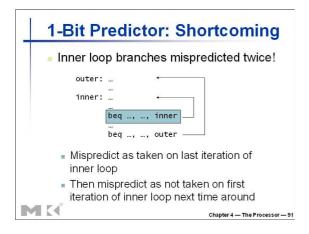

### **Branch Prediction**

- Longer pipelines can't readily determine branch outcome early

- Stall penalty becomes unacceptable

- Predict outcome of branch

- Only stall if prediction is wrong

- In MIPS pipeline

- Can predict branches not taken

- Fetch instruction after branch, with no delay

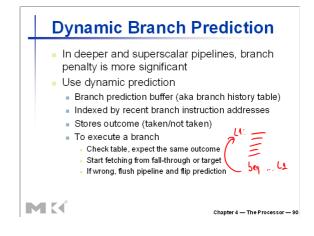

### **More-Realistic Branch Prediction**

- Static branch prediction

- Based on typical branch behavior

- Example: loop and if-statement branches

- Predict backward branches taken

- Predict forward branches not taken

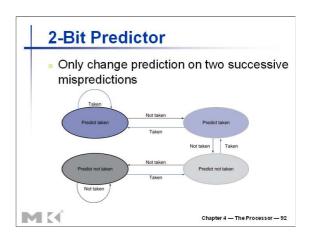

- Dynamic branch prediction

- Hardware measures actual branch behavior

- e.g., record recent history of each branch

- Assume future behavior will continue the trend

- When wrong, stall while re-fetching, and update history

Chapter 4 — The Processor — 47

## **Pipeline Summary**

### The BIG Picture

- Pipelining improves performance by increasing instruction throughput

- Executes multiple instructions in parallel

- Each instruction has the same latency

- Subject to hazards

- Structure, data, control

- Instruction set design affects complexity of pipeline implementation

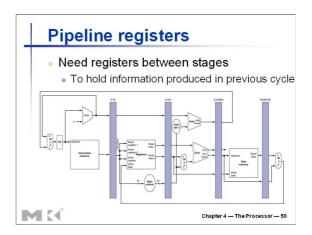

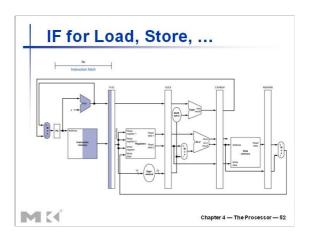

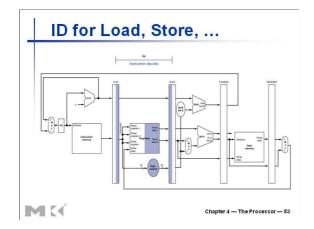

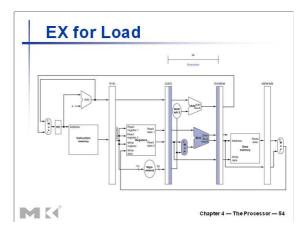

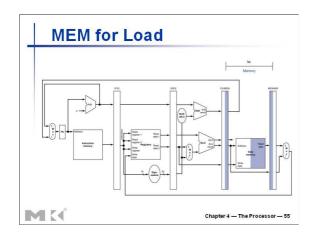

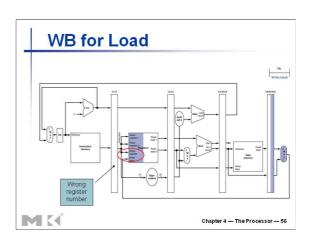

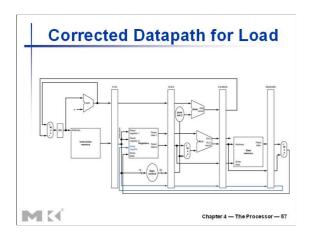

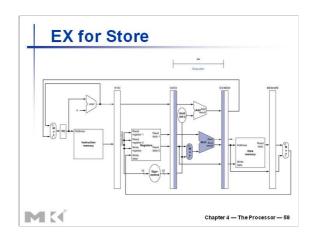

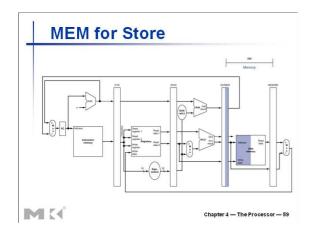

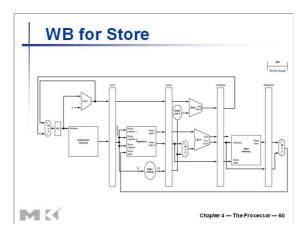

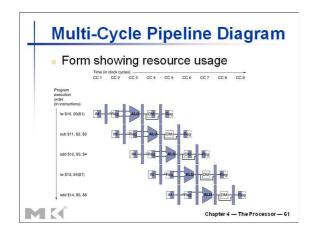

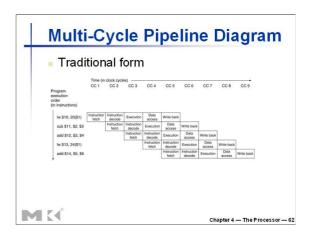

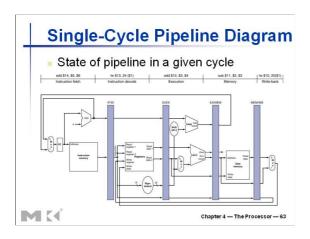

# Pipeline Operation Cycle-by-cycle flow of instructions through the pipelined datapath "Single-clock-cycle" pipeline diagram Shows pipeline usage in a single cycle Highlight resources used c.f. "multi-clock-cycle" diagram Graph of operation over time We'll look at "single-clock-cycle" diagrams for load & store

Chapter 4 — The Processor — 51

MK

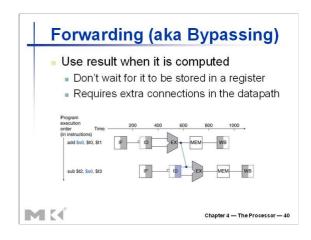

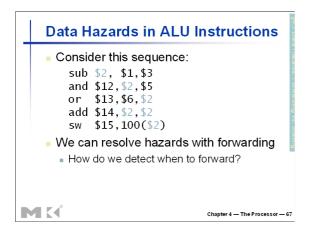

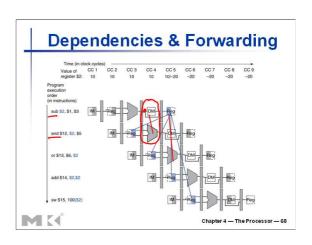

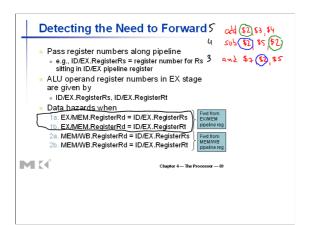

### **Detecting the Need to Forward**

- But only if forwarding instruction will write to a register!

- EX/MEM.RegWrite, MEM/WB.RegWrite

- And only if Rd for that instruction is not \$zero

- EX/MEM.RegisterRd ≠ 0, MEM/WB.RegisterRd ≠ 0

Chapter 4 — The Processor — 70

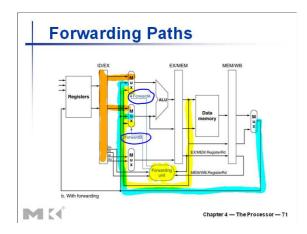

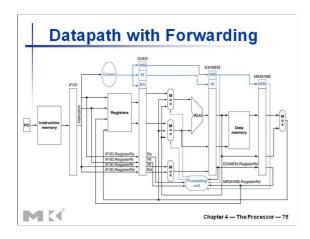

# **Forwarding Conditions**

- EX hazard

- if (EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0) and (EX/MEM.RegisterRd = ID/EX.RegisterRs))

ForwardA = 10

- if (EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0) and (EX/MEM.RegisterRd = ID/EX.RegisterRt)) ForwardR = 10

- MEM hazard

- if (MEM/WB.RegWrite and (MEM/WB.RegisterRd ≠ 0) and (MEM/WB.RegisterRd = ID/EX.RegisterRs))

Forward = 04

- if (MEM/WB.RegWrite and (MEM/WB.RegisterRd ≠ 0) and (MEM/WB.RegisterRd = ID/EX.RegisterRt)) ForwardR = 01

Chapter 4 — The Processor — 72

### **Double Data Hazard**

Consider the sequence:

add \$1,\$1,\$2 add \$1,\$1,\$3 add \$1,\$1,\$4

- Both hazards occur

- Want to use the most recent

- Revise MEM hazard condition

- Only fwd if EX hazard condition isn't true

### **Revised Forwarding Condition**

- MEM hazard

- if (MEM/WB.RegWrite and (MEM/WB.RegisterRd ≠ 0)

and not (EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0) and (EX/MEM.RegisterRd = ID/EX.RegisterRs))

and (MEM/WB.RegisterRd = ID/EX.RegisterRs))

ForwardA = 01

if (MEM/WB.RegWrite and (MEM/WB.RegisterRd ≠ 0)

and not (EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0) and (EX/MEM.RegisterRd = ID/EX.RegisterRt))

and (MEM/WB.RegisterRd = ID/EX.RegisterRt))

ForwardB = 01

MK

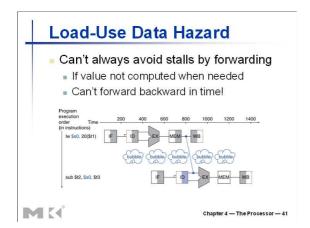

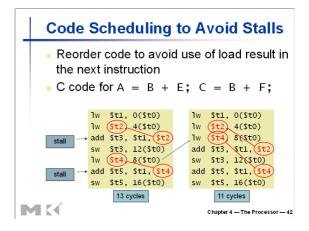

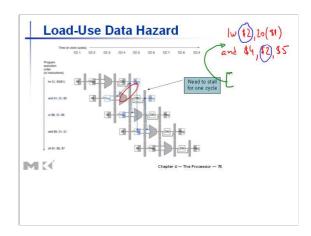

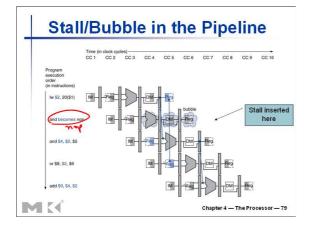

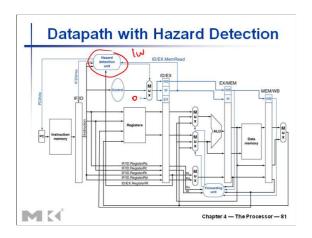

### **Load-Use Hazard Detection**

- Check when using instruction is decoded in ID stage

- ALU operand register numbers in ID stage are given by

- IF/ID.RegisterRs, IF/ID.RegisterRt

- Load-use hazard when

- ID/EX.MemRead and ((ID/EX.RegisterRt = IF/ID.RegisterRs) or (ID/EX.RegisterRt = IF/ID.RegisterRt))

- If detected, stall and insert bubble

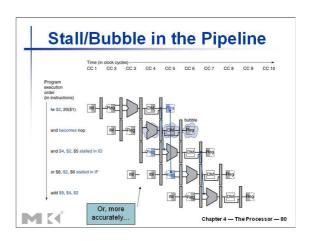

# How to Stall the Pipeline

- Force control values in ID/EX register to 0

- EX, MEM and WB do nop (no-operation)

- Prevent update of PC and IF/ID register

- Using instruction is decoded again

- Following instruction is fetched again

- 1-cycle stall allows MEM to read data for \( \frac{1}{W} \)

- Can subsequently forward to EX stage

# **Calculating the Branch Target**

- Even with predictor, still need to calculate the target address

- 1-cycle penalty for a taken branch

- Branch target buffer

- Cache of target addresses

- Indexed by PC when instruction fetched

- If hit and instruction is branch predicted taken, can fetch target immediately

Chapter 4 — The Processor — 93

### **Pitfalls**

- Poor ISA design can make pipelining harder

- e.g., complex instruction sets (VAX, IA-32)

- Significant overhead to make pipelining work

- IA-32 micro-op approach

- e.g., complex addressing modes

- Register update side effects, memory indirection

- e.g., delayed branches

- Advanced pipelines have long delay slots

Chapter 4 — The Processor — 130

# **Concluding Remarks**

- ISA influences design of datapath and control

- Datapath and control influence design of ISA

- Pipelining improves instruction throughput using parallelism

- More instructions completed per second

- Latency for each instruction not reduced

- Hazards: structural, data, control