# Chapter 2 Conjunto de Instruções ~ Assembly MIPS 286

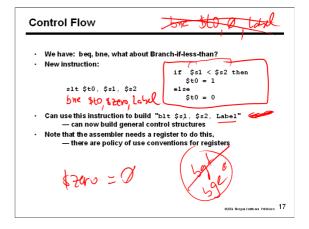

### **Policy of Use Conventions**

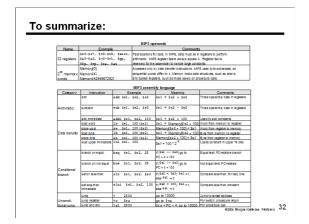

| Name      | Register number | Usage                                        |  |  |

|-----------|-----------------|----------------------------------------------|--|--|

| \$zero    | 0               | the constant value 0                         |  |  |

| \$v0-\$v1 | 2-3             | values for results and expression evaluation |  |  |

| \$a0-\$a3 | 4-7             | arguments                                    |  |  |

| \$t0-\$t7 | 8-15            | temporaries                                  |  |  |

| \$s0-\$s7 | 16-23           | saved                                        |  |  |

| \$t8-\$t9 | 24-25           | more temporaries                             |  |  |

| \$gp      | 28              | global pointer                               |  |  |

| \$sp      | 29              | stack pointer                                |  |  |

| \$fp      | 30              | frame pointer                                |  |  |

| \$ra      | 31              | return address                               |  |  |

Register 1 (\$at) reserved for assembler, 26-27 for operating system

eccot Morgan Farman Petitism 18

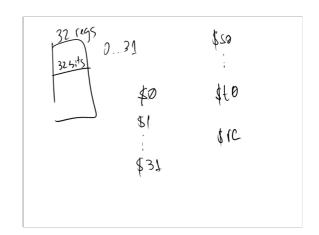

### **Constants**

• Small constants are used quite frequently (50% of operands)

e.g., A = A + 5;

B = B + 1;

C = C - 18;

- · Solutions? Why not?

- put 'typical constants' in memory and load them.

- create hard-wired registers (like \$zero) for constants like one.

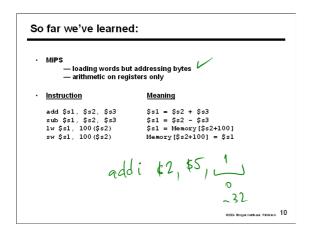

- · MIPS Instructions:

addi \$29, \$29, 4 slti \$8, \$18, 10 andi \$29, \$29, 6 ori \$29, \$29, 4

· Design Principle: Make the common case fast. Which format?

eccos Morgan Fartham Publishers 19

# How about larger constants?

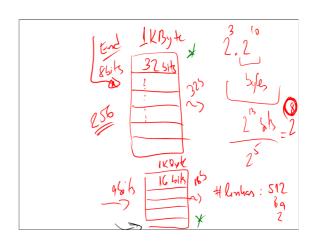

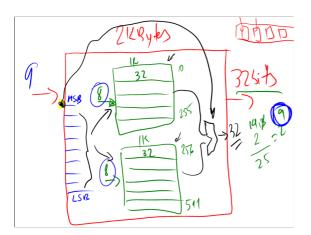

- We'd like to be able to load a 32 bit constant into a register

- · Must use two instructions, new "load upper immediate" instruction

lui \$t0, 1010101010101010 1010101010101010 000000000000000000

· Then must get the lower order bits right, i.e.,

ori \$t0, \$t0, 1010101010101010

1010101010101010 00000000000000000 0000000000000000 1010101010101010 1010101010101010 | 1010101010101010

80004 Morgan Farthaus Pitchtoric 20

# Assembly Language vs. Machine Language

- · Assembly provides convenient symbolic representation

- much easier than writing down numbers

- e.g., destination first

- Machine language is the underlying reality

- e.g., destination is no longer first

- · Assembly can provide 'pseudoinstructions'

- e.g., "move \$t0, \$t1" exists only in Assembly

- would be implemented using "add \$t0,\$t1,\$zero"

- · When considering performance you should count real instructions

00004 Morgan Farman Publishers 21

# Other Issues

· Discussed in your assembly language programming lab:

support for procedures linkers, loaders, memory layout stacks, frames, recursion manipulating strings and pointers interrupts and exceptions system calls and conventions

- · Some of these we'll talk more about later

- $\cdot$  We'll talk about compiler optimizations when we hit chapter 4.

eccol Morgan Farthau Peblishers 22

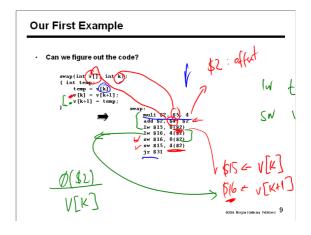

# **Procedimentos**

- Passos a serem executados pelo programa:

- Colocar os parametros em um lugar onde o procedimento consegue recebe-los

Transferir o controle para o procedimento

- Alocar recursos para o procedimento

Executar o procedimento

- Colocar os resultados em um lugar onde o programa possa acessar

- 6. Retornar ao ponto seguinte da chamada do procedimento

- Novidades

- Instrução jal chama o procedimento

Instrução jr retorna do procedimento

- Registrador \$ra contém o valor de retorno

ecco4 Morgan Farthrain Printings 23

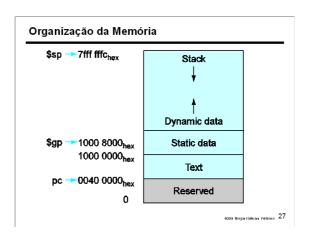

# Pilha • Utiliza o registrador \$sp e \$fp (em alguns casos) Cresce do endereço alto para o endereço baixo Utilizada para guardar valores, variáveis locais e passagem de parâmetros extras Contents of register \$10 Contents of register \$s0 sa Parman Piblishes 24

```

Exemplo

int fact(int n)

if (n < 1)

return 1;

return (n * fact(n - 1);

ecool Morgan Farmann Publishers 25

```

# Exercício 2.29 Coloque comentários no código MIPS abaixo e descreva em uma frase o que ele computa. \$a0 e \$a1 são usados como entrada e contém, respectivamente, os inteiros a e b. \$v0 é usado como saída. add \$t0, \$zero, \$zero loop: beq \$a1, \$zero, finish add \$t0, \$t0, \$a0 sub \$a1, \$a1, 1 loop \$t0, \$t0, 100 finish: addi add \$v0, \$t0, \$zero ecco4 Morgan Farthaus Petitebess 26

# Caracteres

- Representação ASCII x Unicode

- · Representações para strings

- 1. Primeiro caracter indica o tamanho da string

- 2. Uma variável acompanha a string indicando seu tamanho (como numa estrutura)

- 3. A string termina com um caracter reservado

- Instruções

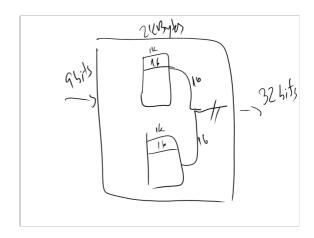

- Byte: Ib e sb (8 bits)

- Halfword: Ih e sh (16 bits)

eccol Morgan Farmann Publishers 28

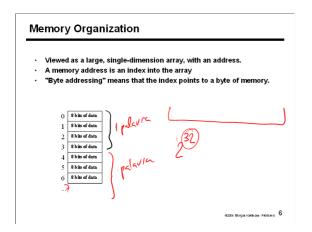

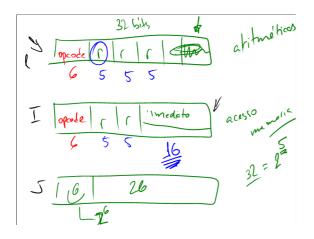

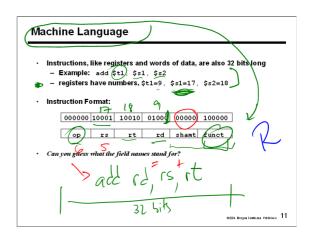

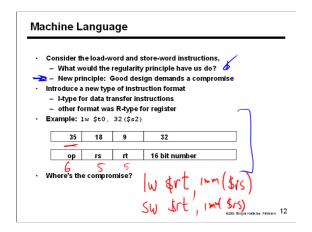

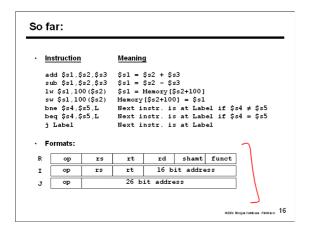

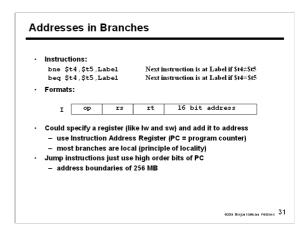

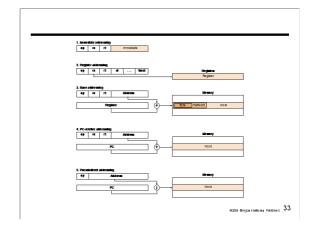

# Overview of MIPS

- · simple instructions all 32 bits wide

- very structured, no unnecessary baggage

- only three instruction formats

|     |                |   |      |              | funct                |  |

|-----|----------------|---|------|--------------|----------------------|--|

| p r | s r            | t | 16 b | it addre     | ss                   |  |

| p   | 26 bit address |   |      |              |                      |  |

|     | p r            |   |      | p 13 10 10 B | p 15 10 10 bit addit |  |

- rely on compiler to achieve performance

what are the compiler's goals?

- · help compiler where we can

eccol Morgan Fartmann Petetshess 29

#

### **Alternative Architectures**

- · Design alternative:

- provide more powerful operations

- goal is to reduce number of instructions executed

- danger is a slower cycle time and/or a higher CPI

- -"The path toward operation complexity is thus fraught with peril. To avoid these problems, designers have moved toward simpler instructions"

- · Let's look (briefly) at IA-32

eccol Morgan Farmann Publishers 36

### IA - 32

- 1978: The Intel 8086 is announced (16 bit architecture)

1980: The 8087 floating point coprocessor is added

1982: The 80286 increases address space to 24 bits, +instructions

1985: The 80386 extends to 32 bits, new addressing modes

1989-1995: The 80486, Pentium, Pentium Pro add a few instructions (mostly designed for higher performance)

1997: 57 new "MMX" instructions are added, Pentium II

1999: The Pentium III added another 70 instructions (SSE)

2001: Another 144 instructions (SSE2)

- 2001: Another 144 instructions (SSE2)

2003: AMD extends the architecture to increase address space to 64 bits, widens all registers to 64 bits and other changes (AMD64)

2004: Intel capitulates and embraces AMD64 (calls it EM64T) and adds more media extensions

- · "This history illustrates the impact of the "golden handcuffs" of compatibility

- "adding new features as someone might add clothing to a packed bag"

- "an architecture that is difficult to explain and impossible to love"

#### IA-32 Overview

- · Complexity:

- Instructions from 1 to 17 bytes long

- one operand must act as both a source and destination

- one operand can come from memory

- complex addressing modes

e.g., "base or scaled index with 8 or 32 bit displacement"

- Saving grace:

- the most frequently used instructions are not too difficult to build

- compilers avoid the portions of the architecture that are slow

"what the \$0x86 lacks in style is made up in quantity, making it beautiful from the right perspective"

ecco4 Morgan Farthaus Petitistess 38

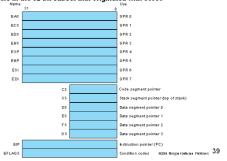

# IA-32 Registers and Data Addressing

# IA-32 Register Restrictions

· Registers are not "general purpose" – note the restrictions below

| Mode                                                     | Description                                                                                                 | Register restrictions           | MIPS equivalent                                                    |  |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------|--|

| Register Indirect                                        | Address is in a register.                                                                                   | not ESP or EBP                  | lw \$s0,0(\$s1)                                                    |  |

| Based mode with 8- or 32-bit displacement                | Address is contents of base register plus<br>displacement.                                                  | not ESP or EBP                  | lw \$s0,100(\$s1)#≤16-bit<br>#displacement                         |  |

| Base plus scaled Index                                   | The address is  Base + (2 <sup>Scale</sup> x Index)  where Scale has the value 0, 1, 2, or 3.               | Base; any GPR<br>Index: not ESP | mul \$t0.\$s2.4<br>add \$t0.\$t0.\$s1<br>lw \$s0.0(\$t0)           |  |

| Base plus scaled Index with<br>8- or 32-bit displacement | The address is  Base + (2 <sup>Scale</sup> x Index) + displacement where Scale has the value 0, 1, 2, or 3. | Base: any GPR<br>Index: not ESP | mal \$t0,\$s2,4<br>add \$t0,\$t0,\$s1<br>lw \$s0,100(\$t0)#≤16-bit |  |

60004 Morgan Farthann Peterses 40

# **IA-32 Typical Instructions**

- Four major types of integer instructions:

- Data movement including move, push, pop

- Arithmetic and logical (destination register or memory)

Control flow (use of condition codes / flags )

- String instructions, including string move and string compare

| Instruction       | Function                                                        |  |  |

|-------------------|-----------------------------------------------------------------|--|--|

| JE name           | if equal(condition code) (EIP=name);<br>EIP-128≤ name < EIP+128 |  |  |

| JMP name          | E IP=name                                                       |  |  |

| CALL name         | SP=SP-4; M[SP]=E1P+5; EIP=name;                                 |  |  |

| MOVW EBX.[EDI+45] | EBX=M[EDI+45]                                                   |  |  |

| PUSH ESI          | SP=SP-4; M(SP)=ESI                                              |  |  |

| POP EDI           | EDI=M[SP]; SP=SP+4                                              |  |  |

| ABB EAX.#6765     | EAX= EAX+6765                                                   |  |  |

| TEST EDX,#42      | Set condition code (flags) with EDX and 42                      |  |  |

| MOVSL             | M[ED]]=M[ES]];<br>EDI=EDI+4; ESI=ESI+4                          |  |  |

FIGURE 2.43 Some typical IA-32 instructions and their functions. A list of frequent opera appears in Figure 2.44. The CALL saves the EIP of the next instruction on the stack. (EIP is the Intel PC.)

eccol Morgan Fartmans Publishers 41

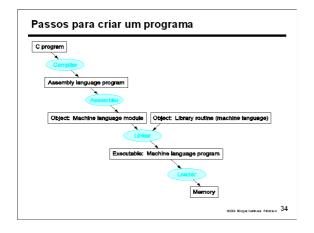

# IA-32 instruction Formats · Typical formats: (notice the different lengths) a.JE EP + displacement t t 8 JE Condition Displacement S. PUSH ESI 5 3 PUSH Reg e ADD EAX, AERE L 3 1 ADD Reg II eccol Morgan Farthann Publishes 42

# Summary

- Instruction complexity is only one variable

lower instruction count vs. higher CPI / lower clock rate

Design Principles:

- simplicity favors regularity

smaller is faster

- sinaier is laster

good design demands compromise

make the common case fast

Instruction set architecture

a very important abstraction indeed!

eccot Morgan Farman Publishes 43