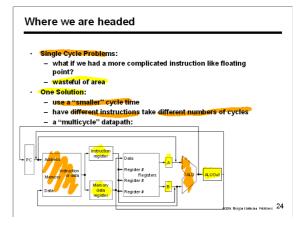

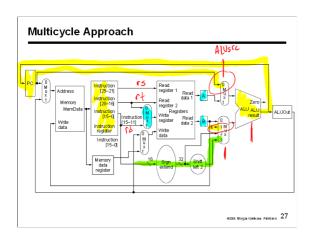

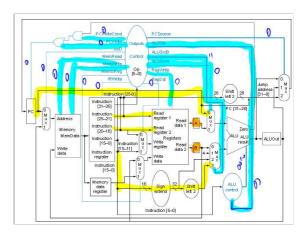

### Multicycle Approach

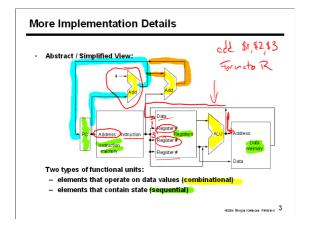

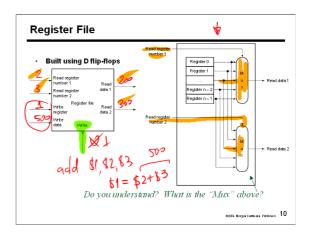

- We will be reusing functional units

- ALU used to compute address and to increment PC

- Memory used for instruction and data

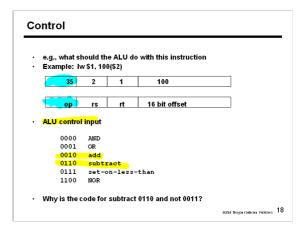

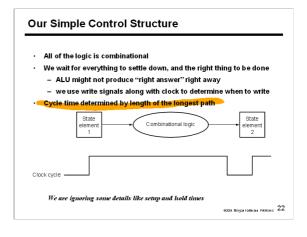

Our control signals will not be determined directly by instruction

- e.g., what should the ALU do for a "subtract" instruction?

- · We'll use a finite state machine for control

eccol Morgan Farman Pictories 25

### Multicycle Approach

- Break up the instructions into steps, each step takes a cycle

- balance the amount of work to be done

- restrict each cycle to use only one major functional unit

- At the end of a cycle

- store values for use in later cycles (easiest thing to do)

- introduce additional "internal" registers

eccol Morgan Farman Publishers 26

eccos Morgan Farman Publishers 28

ecco4 Morgan Farthrain Printings 30

##

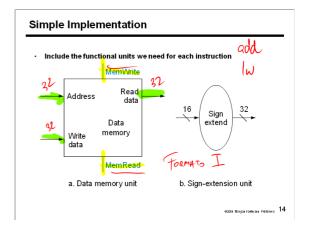

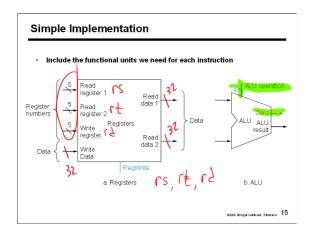

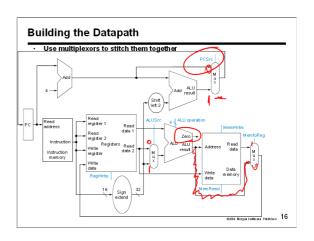

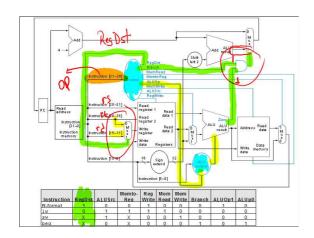

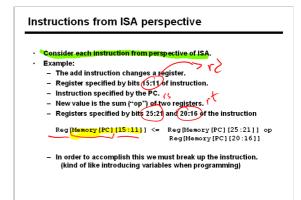

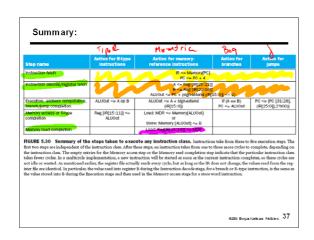

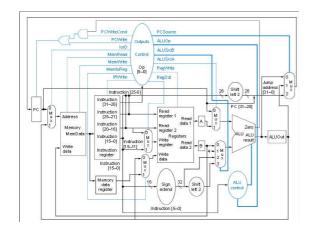

## We define each instruction from the ISA perspective (do this!) Break it down into steps following our rule that data flows through at most one major functional unit (e.g., balance work across steps) Introduce new registers as needed (e.g., A, B, ALUOut, MDR, etc.) Finally try and pack as much work into each step (avoid unnecessary cycles) while also trying to share steps where possible (minimizes control, helps to simplify solution) Result: Our book's multicycle Implementation!

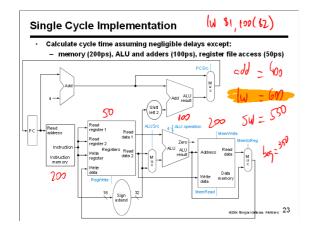

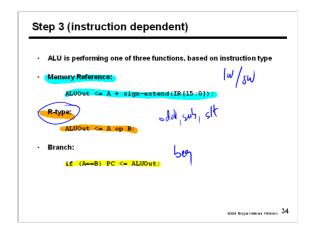

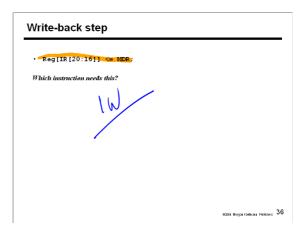

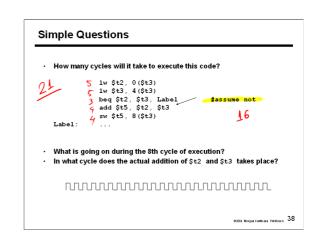

# Five Execution Steps Instruction Fetch Instruction Decode and Register Fetch Execution, Memory Address Computation, or Branch Completion Memory Access or R-type instruction completion Write-back step INSTRUCTIONS TAKE FROM 3 - 5 CYCLES!

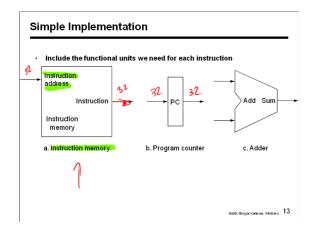

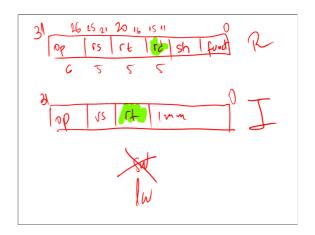

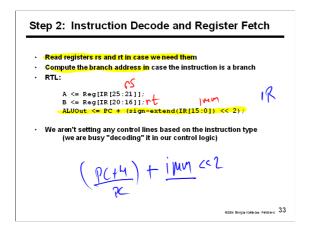

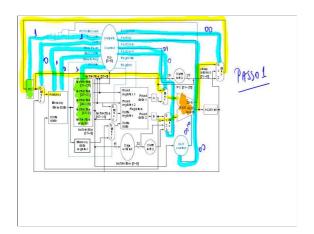

# Step 1: Instruction Fetch Use PC to get instruction and put it in the Instruction Register. Increment the PC by 4 and put the result back in the PC. Can be described succinctly using RTL "Register-Transfer Language" IR <= Memory [PC]; PC <= PC + 4; Can we figure out the values of the control signals? What is the advantage of updating the PC now?

##

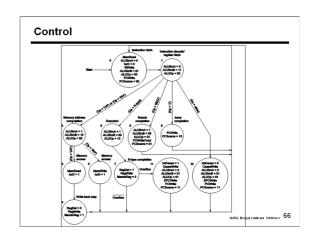

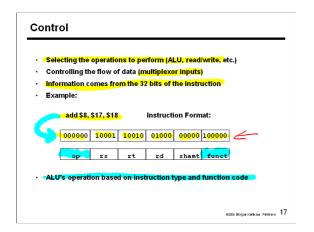

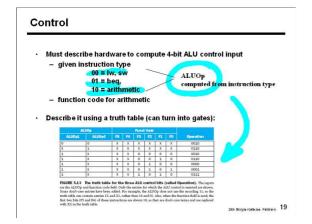

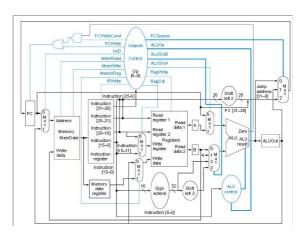

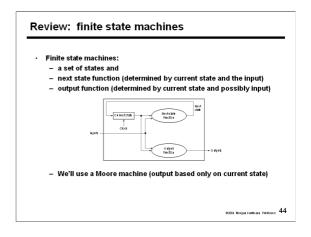

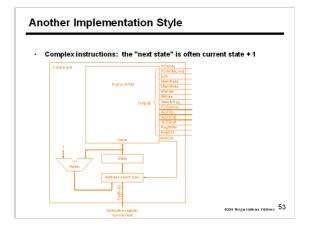

### Implementing the Control

- Value of control signals is dependent upon:

- what instruction is being executed

- which step is being performed

- · Use the information we've accumulated to specify a finite state machine

- specify the finite state machine graphically, or

- use microprogramming

- Implementation can be derived from specification

eccol Morgan Partmann Publishes 46

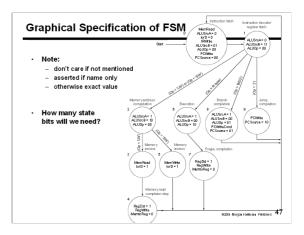

### **Finite State Machine for Control**

· Implementation:

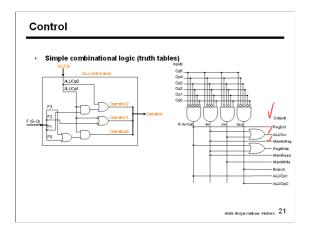

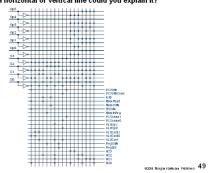

### **PLA Implementation**

· If I picked a horizontal or vertical line could you explain it?

### **ROM Implementation**

- · ROM = "Read Only Memory"

- values of memory locations are fixed ahead of time

- A ROM can be used to implement a truth table

if the address is m-bits, we can address 2<sup>m</sup> entries in the ROM.

- our outputs are the bits of data that the address points to.

m is the "height", and n is the "width"

eccol Morgan Farman Petitises 50

### **ROM Implementation**

- How many inputs are there?

6 bits for opcode, 4 bits for state = 10 address lines (i.e., 210 = 1024 different addresses)

- How many outputs are there?

- 16 datapath-control outputs, 4 state bits = 20 outputs

- ROM is 2<sup>10</sup> x 20 = 20K bits (and a rather unusual size)

- Rather wasteful, since for lots of the entries, the outputs are the

- same

i.e., opcode is often ignored

eccol Morgan Farman Publishers 51

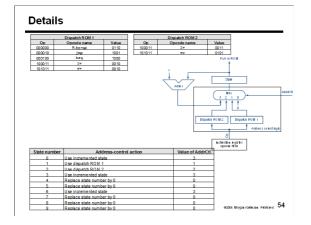

### **ROM vs PLA**

- Break up the table into two parts  $-4\,\text{state bits tell you the 16 outputs},\quad 2^4\,x\,\text{16 bits of ROM}$

- 10 bits tell you the 4 next state bits, 210 x 4 bits of ROM

- Total: 4.3K bits of ROM

- PLA is much smaller

- can share product terms

only need entries that produce an active output

can take into account don't cares

- Size is (#inputs × #product-terms) + (#outputs × #product-terms)

For this example = (10x17)+(20x17) = 510 PLA cells

- · PLA cells usually about the size of a ROM cell (slightly bigger)

eccol Morgan Farthrann Publishers 52

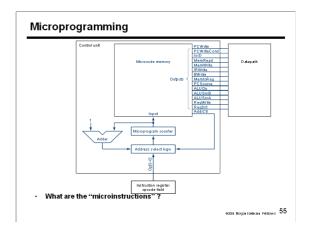

### Microprogramming

- A specification methodology

- appropriate if hundreds of opcodes, modes, cycles, etc.

- signals specified symbolically using microinstructions

| Label    | ALU       | SRC1 | SRC2    | Register<br>control | Memory    | PCWrite<br>control | Sequencing |

|----------|-----------|------|---------|---------------------|-----------|--------------------|------------|

| Fetch    | Add       | PC   | 4       |                     | Read PC   | ALU                | Seq        |

|          | Add       | PC   | Extshft | Read                |           |                    | Dispatch 1 |

| Mem1     | Add       | Α    | Extend  |                     |           |                    | Dispatch 2 |

| LW2      |           |      |         |                     | Read ALU  |                    | Seq        |

|          |           |      |         | Write MDR           |           |                    | Fetch      |

| SW2      |           |      |         |                     | Write ALU |                    | Fetch      |

| Rformat1 | Func code | Α    | В       |                     |           |                    | Seq        |

|          |           |      |         | Write ALU           |           |                    | Fetch      |

| BEQ1     | Subt      | Α    | В       |                     |           | ALUOut-cond        | Fetch      |

| JUMP1    |           |      |         |                     |           | Jump address       | Fetch      |

- Will two implementations of the same architecture have the same microcode?

- What would a microassembler do?

eccol Morgan Farman Petitises 56

| Field name          | Value        | Signals active                | Comment                                                                                                                      |  |  |

|---------------------|--------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

|                     | Add          | ALUOp = 00                    | Cause the ALU to add.                                                                                                        |  |  |

| ALU control         | Subt         | ALUOp = 01                    | Cause the ALU to subtract; this implements the compare for<br>branches.                                                      |  |  |

|                     | Funccode     | ALUOp = 10                    | Use the instruction's function code to determine ALU control.                                                                |  |  |

| SRC1                | PC           | ALUSroA = 0                   | Use the PC as the first ALU input.                                                                                           |  |  |

|                     | A            | ALUSroA = 1                   | Register A is the first ALU input.                                                                                           |  |  |

|                     | В            | ALUSroB = 00                  | Register B is the second ALU input.                                                                                          |  |  |

| SRC2                | 4            | ALUSroB = 01                  | Use 4 as the second ALU input.                                                                                               |  |  |

|                     | Extend       | ALUSrcB = 10                  | Use output of the sign extension unit as the second ALU input.                                                               |  |  |

|                     | Extshft      | ALUSrdB = 11                  | Use the output of the shift-by-two unit as the second ALU input.                                                             |  |  |

|                     | Read         |                               | Read two registers using the rs and rt fields of the IR as the register numbers and outling the data into registers A and B. |  |  |

|                     | Write ALU    | RegWrite,                     | Write a register using the rd field of the IR as the register number and                                                     |  |  |

| Register<br>control |              | RegDst = 1,<br>MembReg = 0    | the contents of the ALUOut as the data.                                                                                      |  |  |

|                     | Write MDR    | RegWrite,<br>RegDst = 0.      | Write a register using the rt field of the IR as the register number and<br>the contents of the MDR as the data              |  |  |

|                     |              | MemtoReg = 1                  |                                                                                                                              |  |  |

|                     | Read PC      | MemRead,<br>lorD = 0          | Read memory using the PC as address; write result into IR (and the MDR)                                                      |  |  |

| Memory              | Read ALU     | MemRead,                      | Read memory using the ALUOut as address; write result into MDR.                                                              |  |  |

|                     | Write ALU    | MemWrite,                     | Write memory using the ALUOut as address, contents of B as the data                                                          |  |  |

|                     | ALU          | PCSource = 00<br>PCWrite      | Write the output of the ALU into the PC.                                                                                     |  |  |

| PC write control    | ALUOut-cond  | PCSource = 01,<br>PCWriteCond | If the Zero output of the ALU is active, write the PC with the contents of the register ALUOut.                              |  |  |

|                     | jump address | PCSource = 10,                | Write the PC with the jump address from the instruction.                                                                     |  |  |

|                     | Sen          | AddrCtl= 11                   | Choose the next microinstruction sequentially.                                                                               |  |  |

| Sequencing          | Fetch        | AddrCtl= 00                   | Go to the first microinstruction to begin a new instruction.                                                                 |  |  |

| order of A          | Dispatch 1   | AddrCtl = 01                  | Dispatch using the ROM 1.                                                                                                    |  |  |

|                     | Dispatch 2   | AddrCtl = 10                  | Dispatch using the ROM 2.                                                                                                    |  |  |

### Maximally vs. Minimally Encoded

- · No encoding:

- 1 bit for each datapath operation

- faster, requires more memory (logic)

- used for Vax 780 an astonishing 400K of memory!

- · Lots of encoding:

- send the microinstructions through logic to get control signals

- uses less memory, slower

- Historical context of CISC:

- Too much logic to put on a single chip with everything else

- Use a ROM (or even RAM) to hold the microcode

- It's easy to add new instructions

eccol Morgan Fartmann Publishers 58

### Microcode: Trade-offs

- · Distinction between specification and implementation is sometimes blurred

- Specification Advantages:

- Easy to design and write

- Design architecture and microcode in parallel

- · Implementation (off-chip ROM) Advantages

- Easy to change since values are in memory

- Can emulate other architectures

- Can make use of internal registers

- · Implementation Disadvantages, SLOWER now that:

- Control is implemented on same chip as processor

- ROM is no longer faster than RAM

- No need to go back and make changes

eccol Morgan Fartham Publishers 59

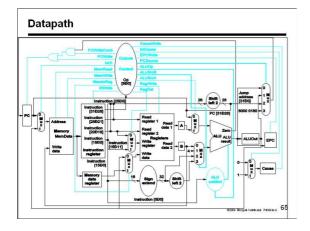

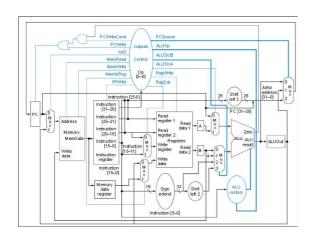

### **Chapter 5 Summary**

- · If we understand the instructions...

- We can build a simple processor!

- · If instructions take different amounts of time, multi-cycle is better

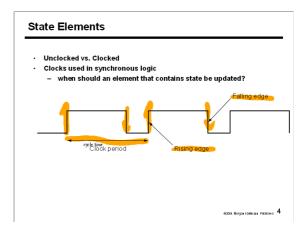

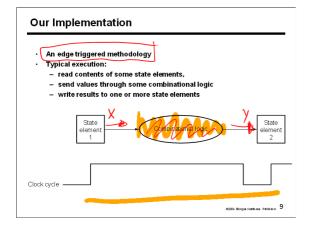

- · Datapath implemented using:

- Combinational logic for arithmetic

- State holding elements to remember bits

- · Control implemented using:

- Combinational logic for single-cycle implementation

- Finite state machine for multi-cycle implementation

ecco4 Morgan Farthaus Petitebes: 63

### Exceptions (MIPS)

- Exception: An unscheduled event that disrupts program execution

- Interrupt: An exception that comes from outside of the processor

- New Registers: EPC and Cause

Two Methods: Simple and Vectored

00004 Morgan Farman Pilitaris 64